Break IC GAL22V10D-10LJ Binary

Break IC GAL22V10D-10LJ Binary

Break IC GAL22V10D-10LJ Binary

Break IC GAL22V10D-10LJ Binary from its memory and rewrite the program into new PLD GAL22V10D:

HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 4 ns Maximum Propagation Delay

— Fmax = 250 MHz

— 3.5 ns Maximum from Clock Input to Data Output

— UltraMOS® Advanced CMOS Technology which has been fully developed in the process of Break IC GAL22V10D-10LJ Binary

· ACTIVE PULL-UPS ON ALL PINS

· COMPATIBLE WITH STANDARD 22V10 DEVICES

— Fully Function/Fuse-Map/Parametric Compatible with Bipolar and UVCMOS 22V10 Devices

· 50% to 75% REDUCTION IN POWER VERSUS BIPOLAR

— 90mA Typical Icc on Low Power Device

— 45mA Typical Icc on Quarter Power Device

· E2 CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

· TEN OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

· PRELOAD AND POWER-ON RESET OF REGISTERS

— 100% Functional Testability

· APPLICATIONS INCLUDE:

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Standard Logic Speed Upgrade

· ELECTRONIC SIGNATURE FOR IDENTIFICATION

The GAL22V10, at 4ns maximum propagation delay time, combines a high performance CMOS process with Electrically Erasable (E2) floating gate technology to provide the highest performance available of any 22V10 device on the market.

CMOS circuitry allows the GAL22V10 to consume much less power when compared to bipolar 22V10 devices. E2 technology offers high speed (<100ms) erase times, providing the ability to reprogram or reconfigure the device quickly and efficiently which is critical for Break IC GAL22V10D-10LJ Binary.

The generic architecture provides maximum design flexibility by allowing the Output Logic Macrocell (OLMC) to be configured by the user. The GAL22V10 is fully function/fuse map/parametric compatible with standard bipolar and CMOS 22V10 devices.

Unique test circuitry and reprogrammable cells allow complete AC, DC, and functional testing during manufacture. As a result, Lattice Semiconductor delivers 100% field programmability and functionality of all GAL products. In addition, 100 erase/write cycles and data retention in excess of 20 years are specified.

Break Microcontroller MSP430F4361 Software

Break Microcontroller MSP430F4361 Software

Break Microcontroller MSP430F4361 Software

MSP430 Microcontrollers (MCUs) from Texas Instruments (TI) are 16-bit, RISC-based, mixed-signal processors designed specifically for ultra-low-power. MSP430 MCUs have the right mix of intelligent peripherals, ease-of-use, low cost and lowest power consumption for thousands of applications which makes it becomes popular to Break Microcontroller MSP430F4361 Software.

TI offers robust design support for the MSP430 MCU platform along with technical documents, training, tools and software to help designers develop products and release them to market faster.

MSP430 Microcontroller DNA

Ultra-Low Power

The MSP430 MCU is designed specifically for ultra-low-power applications. Its flexible clocking system, multiple low-power modes, instant wakeup and intelligent autonomous peripherals enable true ultra-low-power optimization, dramatically extending battery life.

Flexible Clocking System – The MSP430 MCU clock system has the ability to enable and disable various clocks and oscillators which allow the device to enter various low-power modes (LPMs). The flexible clocking system optimizes overall current consumption by only enabling the required clocks when appropriate.

Multiple-Oscillator Clock System

Key Features

· Integrated intelligent peripherals including a wide range of high-performance analog and digital peripherals that off-load the CPU

· Easy-to-use 16-bit RISC CPU architecture enables new applications with industry-leading code density.

· Complete development ecosystem with tools starting at $4.30

400+ Ultra-Low-Power Devices

8-MHz to 25-MHz CPU Speed

0.5KB to 256KB Flash

128B to 18KB RAM

14 to 113 pins; 25+ packages

Sub-Main Clock (SMCLK) – Source for faster individual peripheral modules that may be driven by the internal DCO up to 25 MHz or with external crystal.

Instant Wakeup – The MSP430 MCU can wake-up instantly from LPMs. This ultra-fast wake-up is enabled by the MSP430 MCU’s internal digitally controlled oscillator (DCO), which can source up to 25 MHz and be active and stable in 1µs. Instant wake-up functionality is important in ultra-low-power applications since it allows the microcontroller to use the CPU in very efficient bursts and spend more time in LPMs and provide a better chance to Break Microcontroller MSP430F4361 Software.

Zero-Power Brown-Out Reset (BOR) – The MSP430 MCU’s BOR is always enabled and active in all modes of operation.

the most reliable performance possible while maintaining ultra-low-power consumption. The BOR circuit detects low supply voltages and Lower-Power Peripherals resets the device when power is applied or removed. This functionality is especially critical in battery-powered applications.

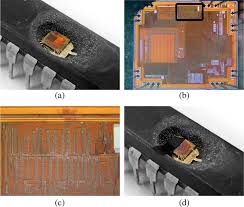

Recover IC PIC16C74 Code

Recover IC PIC16C74 Code

A variety of frequency ranges and packaging options are available when Recover IC PIC16C74 Code. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C7X Product Identification System section at the end of this data sheet.

When placing orders, please use that page of the data sheet to specify the correct part number.

Recover IC PIC16C74 Code

For the PIC16C7X family, there are two device “types” as indicated in the device number:

1. C, as in PIC16C74. These devices have EPROM type memory and operate over the standard voltage range.

2. LC, as in PIC16LC74. These devices have EPROM type memory and operate over an extended voltage range.

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes to Recover IC PIC16C74 Code. Microchip’s PICSTART® Plus and PRO MATE® II programmers both support programming of the PIC16C7X.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory.

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential. Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

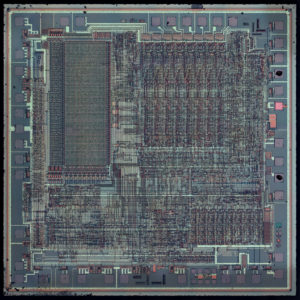

Copy MCU PIC16C72 Software

Copy MCU PIC16C72 Software

We can Copy MCU PIC16C72 Software, please see the MCU PIC16C72 features for your reference:

PIC16C7X Microcontroller Core Features:

· High-performance RISC CPU

· Only 35 single word instructions to learn

· All single cycle instructions except for program branches which are two cycle

· Operating speed: DC – 20 MHz clock input DC – 200 ns instruction cycle

· Up to 8K x 14 words of Program Memory, up to 368 x 8 bytes of Data Memory (RAM)

· Interrupt capability

· Eight level deep hardware stack

· Direct, indirect, and relative addressing modes

· Power-on Reset (POR)

Copy MCU PIC16C72 Software

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Programmable code-protection

· Power saving SLEEP mode

· Selectable oscillator options

· Low-power, high-speed CMOS EPROM technology

· Fully static design

· Wide operating voltage range: 2.5V to 6.0V

· High Sink/Source Current 25/25 mA

· Commercial, Industrial and Extended temperature ranges

· Low-power consumption:

· < 2 mA @ 5V, 4 MHz

· 15 µA typical @ 3V, 32 kHz

· < 1 µA typical standby current

PIC16C7X Peripheral Features:

· Timer0: 8-bit timer/counter with 8-bit prescaler

· Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep via external crystal/clock

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Capture, Compare, PWM module(s)

· Capture is 16-bit, max. resolution is 12.5 ns, Compare is 16-bit, max. resolution is 200 ns, PWM max. resolution is 10-bit from Copy MCU PIC16C72 Software

· 8-bit multichannel analog-to-digital converter

· Synchronous Serial Port (SSP) with SPI and I2C

· Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

· Parallel Slave Port (PSP) 8-bits wide, with external RD, WR and CS controls

· Brown-out detection circuitry for Brown-out Reset (BOR)

Break MCU PIC16C717 Program

Break MCU PIC16C717 Program

We can Break MCU PIC16C717 Program, please view the MCU PIC16C717 features for your reference:

MCU Core Features:

· High-performance RISC CPU

· Only 35 single word instructions to learn

· All single cycle instructions except for program branches which are two cycle

· Operating speed: DC – 20 MHz clock input

· Interrupt capability (up to 10 internal/external interrupt sources)

· Eight level deep hardware stack

· Direct, indirect and relative addressing modes

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Selectable oscillator options:

– INTRC – Internal RC, dual speed (4MHz and 37KHz) dynamically switchable for power savings and Break MCU PIC16C717 Program

– ER – External resistor, dual speed (user selectable frequency and 37KHz) dynamically switchable for power savings

– EC – External clock

– HS – High speed crystal/resonator

– XT – Crystal/resonator

– LP – Low power crystal

Break MCU PIC16C717 Program

· Low-power, high-speed CMOS EPROM technology

· In-Circuit Serial Programming™ (ISCP)

· Wide operating voltage range: 2.5V to 5.5V

· 15 I/O pins with individual control for:

– Direction (15 pins)

– Digital/Analog input (6 pins)

– PORTB interrupt on change (8 pins)

– PORTB weak pull-up (8 pins)

– High voltage open drain (1 pin)

· Commercial and Industrial temperature ranges

· Low-power consumption:

– < 2 mA @ 5V, 4 MHz

– 22.5 µA typical @ 3V, 32 kHz

· Timer0: 8-bit timer/counter with 8-bit prescaler

· Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep via external crystal/clock

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Enhanced Capture, Compare, PWM (ECCP) module

– Capture is 16 bit, max. resolution is 12.5 ns

– Compare is 16 bit, max. resolution is 200 ns

– PWM max. resolution is 10 bit

– Enhanced PWM:

– Single, Half-Bridge and Full-Bridge output modes by Break MCU PIC16C717 Program

– Digitally programmable deadband delay

· Analog-to-Digital converter:

– PIC16C770/771 12-bit resolution

– PIC16C717 10-bit resolution

· On-chip absolute bandgap voltage reference generator

· Programmable Brown-out Reset (PBOR) circuitry

· Programmable Low-Voltage Detection (PLVD) circuitry

· Master Synchronous Serial Port (MSSP) with two modes of operation:

– 3-wire SPI™ (supports all 4 SPI modes)

– I2C™ compatible including master mode support only

· Program Memory Break (PMR) capability for look-up table, character string storage and checksum calculation purposes

Break Microcontroller PIC16C716 Heximal

Break Microcontroller PIC16C716 Heximal

There are two memory blocks in each of these PICmicro® microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur which provide necessity for Break Microcontroller PIC16C716 Heximal.

The PIC16C712/716 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

Break Microcontroller PIC16C716 Heximal

The reset vector is at 0000h and the interrupt vector is at 0004h.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special

Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some “high use” special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device.

The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

The STATUS register, shown in Figure 2-4, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory in the process of Break Microcontroller PIC16C716 Heximal. The STATUS register can be the destination for any instruction, as with any other register.

If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register after Break Microcontroller. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution. Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution.

PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

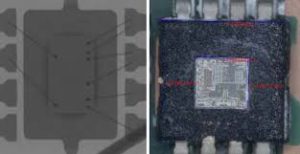

Break Chip PALCE16V8 Software

Break Chip PALCE16V8 Software

The Cypress PALCE16V8 is a CMOS Flash Electrical Erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-product (AND-OR) logic structure and the programmable macrocell which is easier to Break Chip PALCE16V8 Software.

Functional Description (continued)

The PALCE16V8 is executed in a 20-pin 300-mil molded DIP, a 300-mil cerdip, a 20-lead square ceramic leadless chip car-

rier, and a 20-lead square plastic leaded chip carrier. The device provides up to 16 inputs and 8 outputs. The PALCE16V8 can be electrically erased and reprogrammed. The programmable macrocell enables the device to function as a superset to the familiar 20-pin PLDs such as 16L8, 16R8, 16R6, and 16R4.

The PALCE16V8 features 8 product terms per output and 32 input terms into the AND array. The first product term in a macrocell can be used either as an internal output enable control or as a data product term.

Break Chip PALCE16V8 Software

There are a total of 18 architecture bits in the PALCE16V8 macrocell; two are global bits that apply to all macrocells and 16 that apply locally, two bits per macrocell.

The architecture bits determine whether the macrocell functions as a register or combinatorial with inverting or noninverting output. The output enable control can come from an external pin or internally from a product term.

The output can also be permanently enabled, functioning as a dedicated output or permanently disabled, functioning as a dedicated input. Feedback paths are selectable from either the input/output pin associated with the macrocell, the input/output pin associated with an adjacent pin, or from the macrocell register itself to Break Chip PALCE16V8 Software.

Configuration Table

Power-Up Reset

All registers in the PALCE16V8 power-up to a logic LOW for predictable system initialization. For each register, the associated output pin will be HIGH due to active-LOW outputs.

Electronic Signature

An electronic signature word is provided in the PALCE16V8 that consists of 64 bits of programmable memory that can contain user-defined data.

Security Bit

A security bit is provided that defeats the readback of the internal programmed pattern when the bit is programmed.

Low Power

Product Term Disable

Product Term Disable (PTD) fuses are included for each product term. The PTD fuses allow each product term to be individually disabled.

Break IC XC9572-15PQ100C Binary

Break IC XC9572-15PQ100C Binary

We can Break IC XC9572-15PQ100C Binary, below IC XC9572-15PQ100C features for your reference:

Features

7.5 ns pin-to-pin logic delays on all pins fCNT to 125 MHz

72 macrocells with 1,600 usable gates

Up to 72 user I/O pins

5V in-system programmable

Product Specification

Description

The XC9572 is a high-performance CPLD providing advanced in-system programming and test capabilities for general purpose logic integration which is one of the main reasons for its popularity of Break IC XC9572-15PQ100C Binary. It is comprised of eight 36V18 Function Blocks, providing 1,600 usable gates with propagation delays of 7.5 ns. See Figure 2 for the architecture overview.

Break IC XC9572-15PQ100C Binary

– Endurance of 10,000 program/erase cycles

– Program/erase over full commercial voltage and temperature range

Enhanced pin-locking architecture

Flexible 36V18 Function Block

– 90 product terms drive any or all of 18 macrocells within Function Block

– Global and product term clocks, output enables, set and reset signals

Extensive IEEE Std 1149.1 boundary-scan (JTAG) support

Programmable power reduction mode in each macrocell

Slew rate control on individual outputs

User programmable ground pin capability

Extended pattern security features for design protection

High-drive 24 mA outputs

3.3V or 5V I/O capability

Advanced CMOS 5V FastFLASH™ technology

Supports parallel programming of more than one

XC9500 concurrently

Available in 44-pin PLCC, 84-pin PLCC, 100-pin PQFP, and 100-pin TQFP packages

Power Management

Power dissipation can be reduced in the XC9572 by configuring macrocells to standard or low-power modes of operation. Unused macrocells are turned off to minimize power dissipation when Break IC XC9572-15PQ100C Binary.

ICC (mA) = MCHP (1.7) + MCLP (0.9) + MC (0.006 mA/MHz) f

Where:

MCHP = Macrocells in high-performance mode

MCLP = Macrocells in low-power mode

MC = Total number of macrocells used f = Clock frequency (MHz)

Break CPLD EPM7064LC68-15 Binary

Break CPLD EPM7064LC68-15 Binary

We can Break CPLD EPM7064LC68-15 Binary, please view below CPLD EPM7064LC68-15 features for your reference:

Features

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in.

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532 before Break CPLD

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells if Break CPLD

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect) by Break CPLD EPM7064LC68-15 Binary.

Break CPLD EPM7064LC68-15 Binary

PCI-compliant devices available

Altera Corporation

DS-MAX7000-6.7

For information on in-system programmable 3.3-V MAX 7000A or 2.5-V

MAX 7000B devices, see the MAX 7000A Programmable Logic Device Family

Data Sheet or theMAX 7000B Programmable Logic Device Family Data Sheet.

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for IC Break, MCU RECOVER, Chip Recover, Microcontroller Copy service. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice.

Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more information please contact us through email.

Attack CPLD EPM7096QC100-10 Binary

Attack CPLD EPM7096QC100-10 Binary

We can Attack CPLD EPM7096QC100-10 Binary, please view CPLD EPM7096QC100-10 features for your reference:

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect) PCI-compliant devices available.

Open-drain output option in MAX 7000S devices

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable power-saving mode for a reduction of over 50% in each macrocell.

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell 44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages.

Programmable security bit for protection of proprietary designs

– MultiVoltTM I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices (MultiVolt I/O operation is not available in 44-pin packages) – Pin compatible with low-voltage MAX 7000A and MAX 7000B devices.

Enhanced features available in MAX 7000E and MAX 7000S devices

– Six pin- or logic-driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

Attack CPLD EPM7096QC100-10 Binary

– Programmable output slew-rate control

Software design support and automatic place-and-route provided by

Altera’s development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest Programming support.

– Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

– The BitBlasterTM serial download cable, ByteBlasterMVTM parallel port download cable, and MasterBlasterTM serial/universal serial bus (USB) download cable program MAX 7000S devices.