Archive for July, 2012

Flexural Endurance Test after Flexible Circuit Manufacturing

Flexural Endurance Test after Flexible Circuit Manufacturing

GE Research has developed a version of the flexural endurance test based on the IPC standard. Added features to the tester include:

Automated resistivity monitor with threshold

Multiple circuit load (4–up)

Pogo-pin quick connection

Variable-speed motor

Fine-pitch pattern (25mm traces)

Automated data logger

GE Research has also developed a number of TEG monitor cells that are assembled as blocks in a library for use on multiple platforms (RF, DC, analog, PWB, thin core, silicon, etc). The TEG blocks can be assembled in the field area of the panel to aid in process monitoring, second-level assembly, and reliability screening. GE Research has also developed specific tooling to aid in the characterization of thin-core flexible interconnect materials.

Examples of the tools include elongation test stands, flexural endurance systems, and automated electrical testing platforms. The TEG monitors are regularly used in healthcare, military, and commercial flex circuit Manufacturing. These monitors are often used as screening tools for vendor capability demonstrations. Electrical performance, and the corresponding electrical functional testing, is also a critical aspect in flexible printed circuits. Procedures for functional testing are application–specific, but generally, basic function including impedance characterization is tested. Often, users overlook characterization of surface isolation resistance because its adverse impact on electrical performance in low-signal amplitude (microvolts, microamps) applications is not considered or because of the difficulties in obtaining valid data at low-signal amplitudes, especially in the environments required for isolation resistance testing.

Break IC PIC16LF54 Protection

Break IC PIC16LF54 Protection

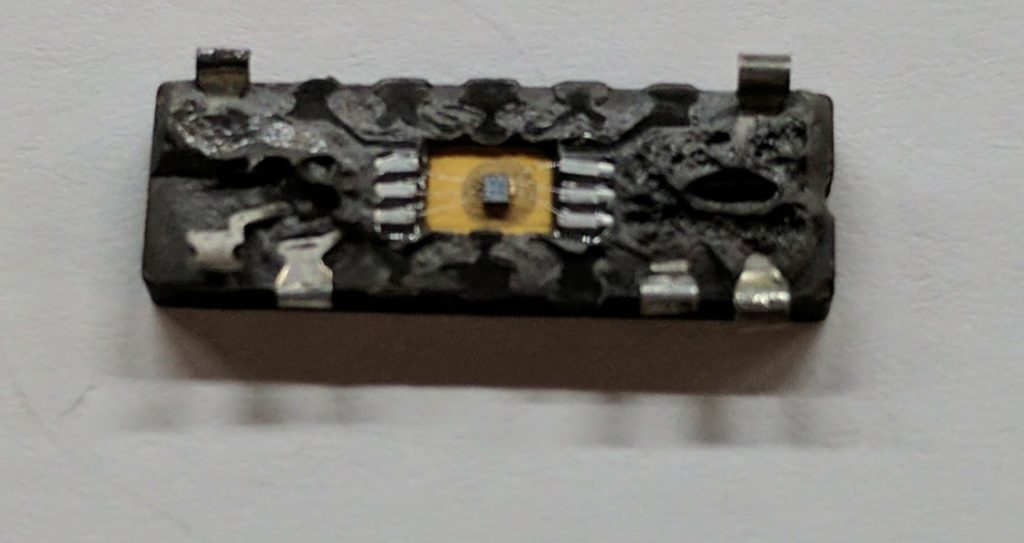

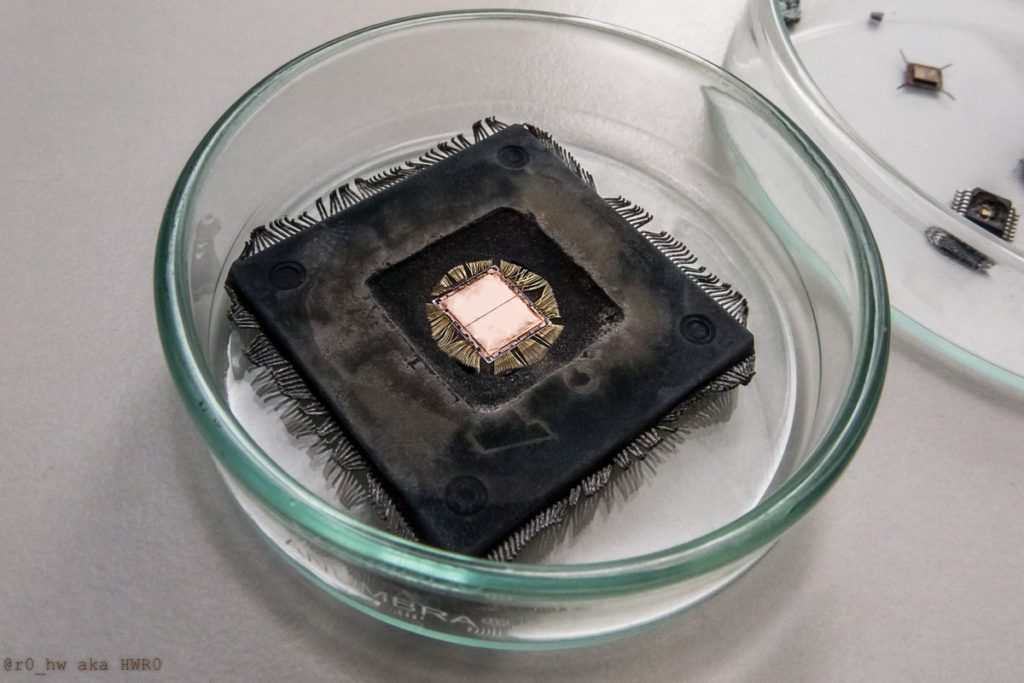

Break IC PIC16LF54 Protection and extract code from MCU PIC16LF54, crack Microcontroller PIC16LF54 fuse bit and decapsulate package;

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical.

For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value if recover chip pic16hv785 hex.

The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented before recover chip pic16c621 program.

Figure 6-4 shows the delay from the external clock edge to the timer incrementing. If the option register is set to read TIMER0 from the pin, the port is forced to an input regardless of the TRIS register setting.

The prescaler assignment is fully under software control (i.e., it can be changed “on the fly” during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT when Break IC pic16f621a program.

The PIC16LF54 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years.

The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h) after recover mcu pic16c622a software.

Unlike the GP0-GP5 that are connected to the I/O pins, SDA and SCL are only connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions;

Decode Locked MCU PIC16F57 Heximal Data

Decode Locked MCU PIC16F57 Heximal Data

Decode Locked MCU PIC16F57 Heximal Data from eeprom memory, unlock microcontroller PIC16F57 security fuse bit and extract firmware out from microprocessor memory;

The Timer0 module has the following features:

8-bit timer/counter register, TMR0

– Readable and writable

8-bit heximal data programmable prescaler

Internal or external clock select

– Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler) if break ic pic16f917 hex.

If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI.

The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in heximal data by the control bit PSA (OPTION<3>) after recover mcu pic16f72 code.

Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,…, 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (TOSC) synchronization when recover mcu pic16f77 eeprom.

Also, there is a delay in the actual incrementing of Timer0 after synchronization. When no prescaler is used, the external clock input is the same as the prescaler output.

The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2TOSC (and a small RC delay of 20 ns) and low for at least 2TOSC (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

Process Challenges and System Applications in Flex Circuit Manufacturing

Process Challenges and System Applications in Flex Circuit Manufacturing

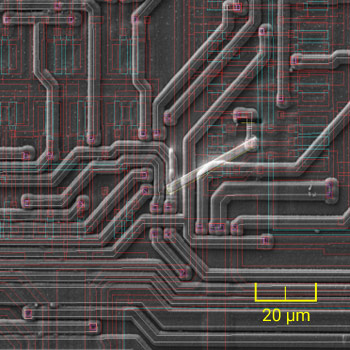

The use of flexible printed circuits has become prevalent in diagnostic imaging systems; in particular, the flex shown in Figure 4 is utilized in an ultrasound probe. The circuit shown has features of 4Mm-thick copper, 25Mm-thick polyimide, conductor pitch of 50Mm, and 25Mm-diameter laser-drilled vias.

Test Element Groups (TEGs) or process monitor coupons are critical components in the fabrication of reliable, high-quality flexible interconnect. TEGs are routinely used for standard process control (SPC), certification of compliance (COC), and reliability or qualification testing. A number of standards can be used for interconnect compliance, such as IPC, JDEC, ASTM, etc. TEGs can be utilized as in-process monitors, for post-fabrication validation, and as reliability screening coupons.

In-process monitoring examples include resistivity or Kelvin test structures to insure metal thickness after plating operations. Four-point probe resistivity measurements can be performed, prior to pattern and etch operations, to measure uniformity of metal deposits. Other in-process coupon examples include lithographic resolution structures (critical dimension measurement vehicles), impedance coupons, elongation/ductility coupons, flexural endurance coupons, and via interconnect strings. Via string coupons allow the manufacturer to test an array of vias (200-500) on the device panel for a measure of via integrity during and after flex circuit manufacturing. Via integrity can be measured by passing current through the via structure to insure that sidewall metal coverage is adequate for the circuit operation environment. The via string can combine all metal layers and metal layer pairs to aid in troubleshooting process fabrication issues (via drilling, via cleaning, via metallization). This coupon allows for circuit troubleshooting and, if performed in-process, can save process time and costs by identifying issues early in a process cycle. Specific via string designs allow for accurate measurements of metal contact resistance.

Reverse Locked IC PIC16F54 Firmware

Reverse Locked IC PIC16F54 Firmware

Reverse Locked IC PIC16F54 manufacturing process and extract IC PIC16F54 Firmware from secured program and data memory by cracking PIC16F54 eeprom and flash memory;

The output driver control register is loaded with the contents of the W register by executing the TRIS instruction. A ‘1’ from a TRIS register bit puts the corresponding output driver in a hi-impedance mode.

A ‘0’ puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register,

A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS registers are “write-only” and are set (output drivers disabled) upon RESET. Some instructions operate internally as read followed by write operations after Recover IC PIC12LC508A eeprom.

The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port example.

a BSF operation on bit5 of GPIO will cause directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the where one or more pins are used as input/outputs if copy protected chip pic16c56 code.

For previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch maybe unknown.

Extract Microprocessor PIC16C58B Data

Extract Microprocessor PIC16C58B Data

Extract Microprocessor PIC16C58B Data from eeprom after unlock microcontroller PIC16C58B secured memory, and copy program pic16c58b into new MCU;

PIC16C58B devices have a 12-bit wide L.I.F.O. hardware push/pop stack. A CALL instruction will push the current value of stack 1 into stack 2 and then push the current data counter value, incremented by one, into stack level 1.

If more than two sequential CALL’s are executed, only the most recent two return addresses are stored. ARETLW instruction will pop the contents of stack level 1 into the data counter and then extract stack level 2 contents into level 1.

If more than two sequential RETLW’s are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction.

This is particularly useful for the implementation of data look-up tables within the data memory. Upon any reset, the contents of the stack remain unchanged, however the data counter (PCL) will also be reset to 0 after copy Microprocessor PIC16F74 code.

The INDF register is not a physical register. Addressing INDF actually addresses the register As with any other register, the I/O register can be written and read under data control.

However, read instructions (e.g., MOVF GPIO,W) always read the I/O pins independent of the pin’s input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set.

See Section 7.0 for SCL and SDA description for PIC16C58B. GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as ‘0’s before break IC PIC16F914 heximal.

Please note that GP3 is an input only pin. The configuration word can set several I/O’s to alternate functions. When acting as alternate functions the pins will read as ‘0’ during port read.

Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

Process Challenges and System Applications in Flexible Printed Circuits

Process Challenges and System Applications in Flexible Printed Circuits

The ability to produce large-area, fine-pitch flexible interconnect is driven by a number of elements. Those elements are comprised of materials, processes, facilities, equipment, design, and engineering support. The demand for thin, fine-pitch flexible interconnect requires unique considerations that are not possible with traditional printed circuit board (PCB) technologies. Fine feature requirements, over large areas, must have clean process facilities and tooling. Most PCB facilities have limited clean-room capabilities and are often restricted to Class 10,000 in the pattern transfer area. Fine-pitch interconnect processing of structures with less than 100um pitch requires clean process areas—i.e., Class 100-1,000–to be able to produce interconnect with acceptable yield. The clean-room facilities must also be augmented with tooling, processes, and operator controls for low-defect densities.

Defects found on flexible interconnect can include trapped fibers, hole in trace, and conductor-to-conductor shorts. These defects are the result of particles generated from process materials or the process environment, including tooling, operators, and the process facility. Many PCB manufacturers have designed clean process tools that contain the work and protect it from an unclean facility.

Flexible printed circuits, with respect to features and process environments, are at the intersection of their semiconductor and printed circuit board equivalents. Fine-pitch flexible interconnect resides at the intersection; tooling, facilities, and expertise from the semiconductor industry are more closely coupled to fine pitch.