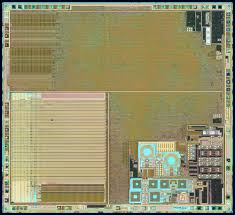

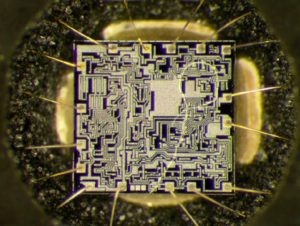

Copy CPLD XC2C128_VQ100 Content

Copy CPLD XC2C128_VQ100 Content

Copy CPLD XC2C128_VQ100 Content

We can Copy CPLD XC2C128_VQ100 Content, please view below CPLD XC2C128_VQ100 features for your reference:

Features

· Optimized for 1.8V systems

– Industry’s fastest low power CPLD

– Densities from 32 to 512 macrocells

· Industry’s best 0.18 micron CMOS CPLD

– Optimized architecture for effective logic synthesis by Copy CPLD XC2C128_VQ100 Content

– Multi-voltage I/O operation — 1.5V to 3.3V

· Advanced system features

– Fastest in system programming

· 1.8V ISP using IEEE 1532 (JTAG) interface

– On-The-Fly Reconfiguration (OTF)

– IEEE1149.1 JTAG Boundary Scan Test

– Optional Schmitt trigger input (per pin)

– Multiple I/O banks on all devices

– Unsurpassed low power management

– SSTL2_1,SSTL3_1, and HSTL_1 on 128 macrocell and denser devices

– Hot pluggable PLA architecture

– Superior pinout retention

– 100% product term routability across function block Wide package availability including fine pitch:

– Chip Scale Package (CSP) BGA, Fine Line BGA, TQFP, PQFP, VQFP, and QFN packages

Free software support for all densities using Xilinx® WebPACK™ tool Industry leading nonvolatile 0.18 micron CMOS

· DataGATE external signal control

– Flexible clocking modes

· Optional DualEDGE triggered registers

· Clock divider (÷ 2,4,6,8,10,12,14,16)

· CoolCLOCK

– Global signal options with macrocell control

· Multiple global clocks with phase selection per macrocell

· Multiple global output enables

· Global set/reset

– Abundant product term clocks, output enables and set/resets

– Efficient control term clocks, output enables and set/resets for each macrocell and shared across function blocks from Copy CPLD XC2C128_VQ100 Content

– Advanced design security

– Open-drain output option for Wired-OR and LED drive

– Optional bus-hold, 3-state or weak pullup on select I/O pins

– Optional configurable grounds on unused I/Os

– Mixed I/O voltages compatible with 1.5V, 1.8V, process

– Guaranteed 1,000 program/erase cycles

– Guaranteed 20 year data retention

Family Overview

Xilinx CoolRunner™-II CPLDs deliver the high speed and ease of use associated with the XC9500/XL/XV CPLD family with the extremely low power versatility of the XPLA3 family in a single MCU Recovery. This means that the exact same parts can be used for high-speed data communications.

computing systems and leading edge portable products, with the added benefit of In System Programming. Low power consumption and high-speed operation are combined into a single family that is easy to use and cost effective. Clocking techniques and other power saving features extend the users’ power budget. The design features are supported starting with Xilinx ISE® 4.1i WebPACK tool.

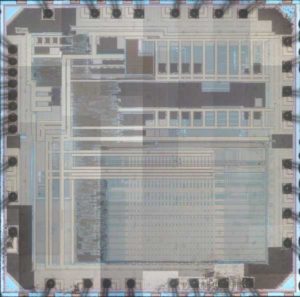

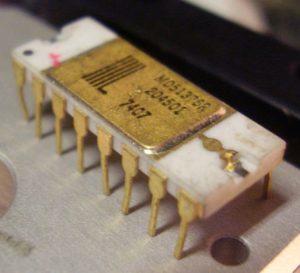

Attack PLD EPM7128ELC84-10 Binary

Attack PLD EPM7128ELC84-10 Binary

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 which has provide convenience for Attack PLD EPM7128ELC84-10 Binary.

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect)

Attack PLD EPM7128ELC84-10 Binary

PCI-compliant devices available

Open-drain output option in MAX 7000S devices

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable power-saving mode for a reduction of over 50% in each macrocell

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages

Programmable security bit for protection of proprietary designs

3.3-V or 5.0-V operation

– MultiVoltTM I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices after Attack PLD EPM7128ELC84-10 Binary (MultiVolt I/O operation is not available in 44-pin packages)

– Pin compatible with low-voltage MAX 7000A and MAX 7000B devices

Enhanced features available in MAX 7000E and MAX 7000S devices

– Six pin- or logic-driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

– Programmable output slew-rate control

Software design support and automatic place-and-route provided by Altera’s development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest.

Programming support

– Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

– The BitBlasterTM serial download cable, ByteBlasterMVTM parallel port download cable, and MasterBlasterTM serial/universal serial bus (USB) download cable program MAX 7000S devices

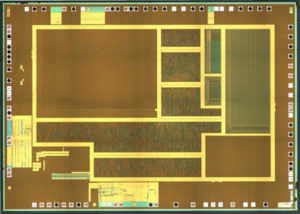

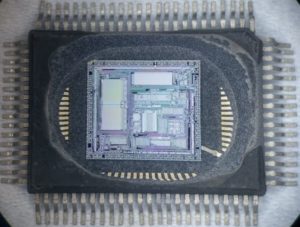

Break CPLD EPM3128ATC100-7 Software

Break CPLD EPM3128ATC100-7 Software

Break CPLD EPM3128ATC100-7 Software

High–performance, low–cost CMOS EEPROM–based programmable logic devices (PLDs) built on a MAX® architecture 3.3-V in-system programmability (ISP) through the built–in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability when Break CPLD EPM3128ATC100-7 Software.

– Enhanced ISP algorithm for faster programming

– ISP_Done bit to ensure complete programming

– Pull-up resistor on I/O pins during in–system programming

High–density PLDs ranging from 600 to 10,000 usable gates 4.5–ns pin–to–pin logic delays with counter frequencies of up to 227.3 MHz

MultiVoltTM I/O interface enabling the device core to run at 3.3 V, while I/O pins are compatible with 5.0–V, 3.3–V, and 2.5–V logic levels

Pin counts ranging from 44 to 256 in a variety of thin quad flat pack (TQFP), plastic quad flat pack (PQFP), plastic J–lead chip carrier (PLCC), and FineLine BGATM packages

Hot–socketing support

Programmable interconnect array (PIA) continuous routing structure for fast, predictable performance.

PCI compatible

Bus–friendly architecture including programmable slew–rate control

Open–drain output option

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable power–saving mode for a power reduction of over 50% in each macrocell

Configurable expander product–term distribution, allowing up to 32 product terms per macrocell

Programmable security bit for protection of proprietary designs which is necessary to be removed when Break CPLD EPM3128ATC100-7 Software

Enhanced architectural features, including:

– 6 or 10 pin– or logic–driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Programmable output slew–rate control

Software design support and automatic place–and–route provided by Altera’s development systems for Windows–based PCs and Sun SPARCstations, and HP 9000 Series 700/800 workstations

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from third–party manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest.

Programming support with the Altera master programming unit (MPU), MasterBlasterTM communications cable, ByteBlasterMVTM parallel port download cable, BitBlasterTM serial download cable as well as programming hardware from third–party manufacturers and any in–circuit tester that supports JamTM Standard Test and Programming Language (STAPL) Files (.jam), Jam STAPL Byte-Code Files (.jbc), or Serial Vector Format Files (.svf).

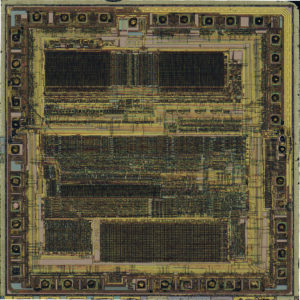

Copy CPLD EPM9320ARC208-10 Binary

Copy CPLD EPM9320ARC208-10 Binary

High-performance CMOS EEPROM-based programmable logic devices (PLDs) built on third-generation Multiple Array MatriX (MAX®) architecture which is the main reason for requirement on Copy CPLD EPM9320ARC208-10 Binary.

Copy CPLD EPM9320ARC208-10 Binary

5.0-V in-system programmability (ISP) through built-in IEEE Std.

1149.1 Joint Test Action Group (JTAG) interface

Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990

High-density erasable programmable logic device (EPLD) family ranging from 6,000 to 12,000 usable gates (see Table 1)

10-ns pin-to-pin logic delays with counter frequencies of up to 144 MHz

Fully compliant with the peripheral component interconnect Special Interest Group’s (PCI SIG) PCI Local Bus Specification, Revision 2.2

Dual-output macrocell for independent use of combinatorial and registered logic

FastTrack® Interconnect for fast, predictable interconnect delays

Input/output registers with clear and clock enable on all I/O pins

Programmable output slew-rate control to reduce switching noise

MultiVolt™ I/O interface operation, allowing devices to interface with 3.3-V and 5.0-V devices

Configurable expander product-term distribution allowing up to 32 product terms per macrocell

Programmable power-saving mode for more than 50% power reduction in each macrocell

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable security bit for protection of proprietary designs which must be disable when Copy CPLD EPM9320ARC208-10 Binary

Software design support and automatic place-and-route

Altera’s MAX+PLUS® II development system on Windows-based PCs as well as Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations

Additional design entry and simulation support provided by EDIF 200 and 300 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest

Programming support with Altera’s Master Programming Unit (MPU), BitBlasterTM serial download cable, ByteBlasterTM parallel port download cable, and ByteBlasterMVTM parallel port download cable, as well as programming hardware from third-party manufacturers.

Offered in a variety of package options with 84 to 356 pins.

Recover Microcontroller PIC16F83 Eeprom

Recover Microcontroller PIC16F83 Eeprom

We can Recover Microcontroller PIC16F83 Eeprom, please view the Microcontroller PIC16F83 features for your reference:

High Performance RISC CPU Features:

• Only 35 single word instructions to learn

• All instructions single cycle except for program branches which are two-cycle Operating speed: DC – 10 MHz clock input

DC – 400 ns instruction cycle

14-bit wide instructions

8-bit wide data path

15 special function hardware registers

Eight-level deep hardware stack

Direct, indirect and relative addressing modes

Four interrupt sources:

– External RB0/INT pin

– TMR0 timer overflow

– PORTB<7:4> interrupt on change

– Data EEPROM write complete

· 1000 erase/write cycles Flash program memory

· 10,000,000 erase/write cycles EEPROM data memory

· EEPROM Data Retention > 40 years

Peripheral Features:

· 13 I/O pins with individual direction control

· High current sink/source for direct LED drive

– 25 mA sink max. per pin

– 20 mA source max. per pin

· TMR0: 8-bit timer/counter with 8-bit programmable prescaler

Special Microcontroller Features:

· In-Circuit Serial Programming (ICSP™) – via two pins (ROM devices support only Data EEPROM programming)

· Power-on Reset (POR)

· Power-up Timer (PWRT)

· Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-Microcontroller RC oscillator for reliable operation

· Code-protection

· Power saving SLEEP mode

· Selectable oscillator options

Low-power, high-speed technology

· Fully static design

· Wide operating voltage range:

– Commercial: 2.0V to 6.0V

– Industrial: 2.0V to 6.0V

· Low power consumption:

– < 2 mA typical @ 5V, 4 MHz

– 15 µA typical @ 2V, 32 kHz

– < 1 µA typical standby current @ 2V

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for IC Read, MCU Recover, Microcontroller Extract, Microcontroller Unlock service. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice. Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more information please contact us through email.

Recover MCU PIC16C71 Code

Recover MCU PIC16C71 Code

The PIC16C71X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family when it becomes necessary to Recover MCU PIC16C71 Code. All PIC16/17 microcontrollers employ an advanced RISC architecture by Break IC TS83C51U2 Binary. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources.

Recover MCU PIC16C71 Code

The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available in the process of Crack MCU Program. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class. The PIC16C71 devices have 36 bytes of RAM, the PIC16C711 has 68 bytes of RAM and the PIC16C715 has 128 bytes of RAM. Each device has 13 I/O pins. In addition a timer/counter is available. Also a 4-channel high-speed 8-bit A/D is provided which provide support for Break IC ATMEGA32A Software.

The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc. The PIC16C71X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption.

There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals only in order to Recover MICROCONTROLLER ATMEGA64PA Binary. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the MCU from SLEEP through several external and internal interrupts and resets.

Recover IC PIC16C554 Software

Recover IC PIC16C554 Software

We can Recover IC PIC16C554 Software, please view the Ic PIC16C554 features for your reference:

High Performance RISC CPU:

· Only 35 instructions to learn

· All single-cycle instructions (200 ns), except for program branches which are two-cycle

· Operating speed:

– DC – 20 MHz clock input

– DC – 200 ns instruction cycle

16 special function hardware registers

Special Ic Features (cont’d)

8-level deep hardware stack

Direct, Indirect and Relative addressing modes by Break MCU ATMEGA64PA Binary,

Programmable code protection

Power saving SLEEP mode

Peripheral Features:

· 13 I/O pins with individual direction control

· High current sink/source for direct LED drive Selectable oscillator options Serial in-circuit programming (via two pins) Four user programmable ID locations

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

Special Ic Features:

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

CMOS Technology:

· Low-power, high-speed CMOS EPROM technology when Break MCU ATMEGA128PA Firmware

· Fully static design

· Wide operating voltage range

– 2.5V to 5.5V PIC16C55X

– 3.0 to 5.5V PIC16C55XA

· Commercial, industrial and extended temperature range

· Low power consumption

– < 2.0 mA @ 5.0V, 4.0 MHz

– 15 µA typical @ 3.0V, 32 kHz

– < 1.0 µA typical standby current @ 3.0V from Break IC ATMEGA128A Firmware

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for IC Read, MCU Crack, MCU Recover, IC Unlock service. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice. Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more

Copy Chip PIC16F74A Binary

Copy Chip PIC16F74A Binary

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses to Copy Chip PIC16F74A Binary. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus.

Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions by Recovery MICROCONTROLLER ATMEGA48A Program. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle.

A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode.

This symmetrical nature and lack of ‘special optimal situations’ make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit to Break MCU ATMEGA168A Flash, It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two’s complement in nature. In two-operand instructions, typically one operand is the working register (W register) from Copy Chip PIC16F74A Binary. The other operand is a file register or an immediate constant.

In single operand instructions, the operand is either the W register or a file register. The W register is an 8-bit working register used for ALU operations. It is not an addressable register. Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register to Recover IC ATMEGA168PA Program. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See theSUBLW and SUBWF instructions for examples after clone IC.

Copy Microcontroller PIC16C770 Eeprom

Copy Microcontroller PIC16C770 Eeprom

We can Copy Microcontroller PIC16C770 Eeprom, please view the Microcontroller PIC16C770 features for your reference:

This document contains device-specific information. Additional information may be found in the PICmicroTM Mid-Range Reference Manual, (DS33023), which may be obtained from your local Micromicrocontroller Sales Representative or downloaded from the Micromicrocontroller website.

The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended copying for a better understanding of the device architecture and operation of the peripheral modules.

There are two memory blocks in each of these PICmicro ® microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur. Additional information on device memory may be found in the PICmicro Mid-Range Reference Manual, (DS33023).

The PIC16C717/770/771 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16C717 and the PIC16C770 have 2K x 14 words of program memory. The PIC16C771 has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound which can facilitate the MCU Cracking.

The reset vector is at 0000h and the interrupt vector is at 0004h. Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers if Copy Microcontroller. Some frequently used special function registers from one bank are mirrored in another bank for code reduction and quicker access.

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

Copy AVR ATmega161 Firmware

Copy AVR ATmega161 Firmware

We can Copy AVR ATMEGA161 Firmware, please view below the feature of AVR ATMEGA161 for our reference:

Features

· High-performance, Low-power AVR® 8-bit Microcontroller

· Advanced RISC Architecture

– 130 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 8 MIPS Throughput at 8 MHz

– On-chip 2-cycle Multiplier

Program and Data Memories

– 16K Bytes of Non-volatile In-System Programmable Flash Endurance: 1,000 Write/Erase Cycles

– Optional Boot Code Memory with Independent Lock bits Self-programming of Program and Data Memories

– 512 Bytes of Non-volatile In-System Programmable EEPROM Endurance: 100,000 Write/Erase Cycles

– 1K Byte of Internal SRAM

– Programming Lock for Software Security

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and PWM

– Expanded 16-bit Timer/Counter System with Separate Prescaler, Compare, Capture Modes and Dual 8-, 9-, or 10-bit PWM after Copy AVR

– Dual Programmable Serial UARTs

– Master/Slave SPI Serial Interface

– Real-time Counter with Separate Oscillator

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

Special Microcontroller Features

– External and Internal Interrupt Sources

– Three Sleep Modes: Idle, Power-save and Power-down Power Comsumption at 4 MHz, 3.0V, 25°C

– Active 3.0 mA

– Idle Mode 1.2 mA

– Power-down Mode < 1 µA

I/O and Packages

– 35 Programmable I/O Lines

– 40-lead PDIP and 44-lead TQFP Operating Voltages

– 2.7V – 5.5V for the ATmega161L

– 4.0V – 5.5V for the ATmega161 Speed Grades

– 0 – 4 MHz for the ATmega161L

– 0 – 8 MHz for the ATmega161

Commercial and Industrial Temperature Ranges