Reverse Engineer ARM STM32F105V8 Microcomputer Program

Reverse Engineer ARM STM32F105V8 Microcomputer Program

Reverse Engineer ARM STM32F105V8 Microcomputer Program can help engineer to extract source code of heximal file from secured microprocessor stm32f105v8, and then copy flash binary software to new stm32f105v8 mcu;

Reverse Engineer ARM STM32F105V8 Microcomputer Program can help engineer to extract source code of heximal file from secured microprocessor stm32f105v8, and then copy flash binary software to new stm32f105v8 mcu

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs after replicating stm32f105r8 mcu chip embedded flash program, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

crack locked microprocessor STM32F105V8 fuse bit and extract embedded source code from mcu chip STM32F105V8

This timer is dedicated for OS, but can be used also as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

Up to two I²C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes. They support dual slave addressing (7-bit only) and both 7/10-bit addressing in master mode to decrypt mcu chip stm32f105vc secured memory binary program. A hardware CRC generation/verification is embedded. They can be served by DMA and they support SM Bus 2.0/PM Bus.

Reverse Encrypted STM32F103VB Microprocessor Protection

Reverse Encrypted STM32F103VB Microprocessor Protection

Reverse Encrypted STM32F103VB Microprocessor Protection and clone stm32f103vb locked mcu flash heximal file, copy flash memory firmware to arm microcontroller stm32f103vb;

Reverse Encrypted STM32F103VB Microprocessor Protection and clone stm32f103vb locked mcu flash heximal file, copy flash memory firmware to arm microcontroller stm32f103vb

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels. It has complementary PWM outputs with programmable inserted dead-times. It can also be seen as a complete general-purpose timer. The 4 independent channels can be used for

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as a general-purpose 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the same architecture. The advanced-control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining to recover stm32f103c6 locked mcu flash full content.

clone STMicroelectronics-STM32F103VB microprocessor flash memory content and copy embedded heximal file and binary program to new mcu chip STMicroelectronics-STM32F103VB

There are up to three synchronizable general-purpose timers embedded in the STM32F103xx performance line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

Desbloquee el microcontrolador de brazo MCU STM32F105VBT6 y lea el firmware integrado heximal de la memoria flash

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation when recovering arm microprocessor stm32f103cb flash program.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from one to three Hall-effect sensors.

Reverse Engineering ARM Microprocessor STM32F103RB Flash Memory

Reverse Engineering ARM Microprocessor STM32F103RB Flash Memory

Reverse Engineering ARM Microprocessor STM32F103RB Flash Memory is a process to crack stm32f103rb secured microcontroller fuse bit and copy the heximal memory firmware to new microcomputer stm32f103rb flash memory;

Reverse Engineering ARM Microprocessor STM32F103RB Flash Memory is a process to crack stm32f103rb secured microcontroller fuse bit and copy the heximal memory firmware to new microcomputer stm32f103rb flash memory

The device has an integrated power-on reset (POR) / power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V to pull out stm32f103t8 microcontroller flash data. The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

unlock STM32F103RB arm microcontroller fuse bit and readout firmware heximal of flash memory of mcu stm32f103rb

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop mode

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode, providing high impedance output. The STM32F103xx performance line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

- Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

- Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped by cracking stm32f103vet7 arm ic mcu flash memory, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

desbloquee la broca del fusible del microcontrolador del brazo STM32F103RB y lea el firmware heximal de la memoria flash de mcu stm32f103rb

Reverse Engineering STM32F103R8 Microcomputer Flash Program

Reverse Engineering STM32F103R8 Microcomputer Flash Program

Reverse Engineering STM32F103R8 Microcomputer Flash Program can help engineer to extract embedded firmware heximal file from secured mcu stm32f103r8 then clone arm microcontroller stm32f103r8 binary data to new Microprocessor;

Reverse Engineering STM32F103R8 Microcomputer Flash Program can help engineer to extract embedded firmware heximal file from secured mcu stm32f103r8 then clone arm microcontroller stm32f103r8 binary data to new Microprocessor

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator when restoring stm32f103c4 arm microcontroller flash binary file. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the high-speed APB domains is 72 MHz. The maximum allowed frequency of the low-speed APB domain is 36 MHz. See Figure 2 for details on the clock tree.

unlock secured STM32F105R8T6 microcontroller fuse bit and extract heximal program file from STM32F105R8T6 microprocessor flash memory

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash

- Boot from System memory

- Boot from embedded SRAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USART1. For further details refer to AN2606, available on www.st.com.

- VDD = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through VDD

- VSSA, VDDA = 2.0 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC is used) by restoring stm32f103c8 microcontroller flash program code. VDDA and VSSA must be connected to VDD and VSS,

- VBAT = 8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when VDD is not present.

For more details on how to connect power pins, refer to Figure 14: Power supply scheme.

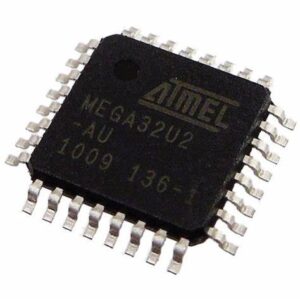

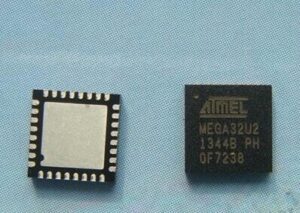

Break Locked ATmega32U2 Microprocessor Flash

Break Locked ATmega32U2 Microprocessor Flash

Break Locked ATmega32U2 Microprocessor Flash and copy heximal firmware to new atmega32u2 flash memory and eeprom memory, the source code of binary program and data will be pull out from original master mcu atmega32u2;

Break Locked ATmega32U2 Microprocessor Flash and copy heximal firmware to new atmega32u2 flash memory and eeprom memory, the source code of binary program and data will be pull out from original master mcu atmega32u2

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. Output from the inverting Oscillator amplifier if enabled by Fuse. Also serves as a generic I/O. This documentation contains simple code examples that briefly show how to use various parts of the device. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documen- tation for more details.

These code examples assume that the part specific header file is included before compilation. For I/O registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

reverse engineering ATMEGA32U2 secured mcu fuse bit and dump firmware binary or heximal out of ATMEGA32U2 flas memory

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories when reversing atmega16u2 microcontroller protection, perform calculations, control peripherals, and handle interrupts.

Break Locked ATmega32U2 Microprocesador Flash y copie el firmware heximal a la nueva memoria flash atmega32u2 y memoria eeprom, el código fuente del programa binario y los datos se extraerán del mcu maestro original atmega32u2

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is prefetched from the program memory after recovering atmega8u2 encrypted microprocessor flash memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

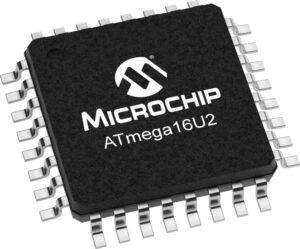

Reverse AVR Microcomputer ATmega16U2 Flash Program

Reverse AVR Microcomputer ATmega16U2 Flash Program

Reverse AVR Microcomputer ATmega16U2 Flash Program and copy atmel avr mcu atmega16u2 firmware to new microcontroller, the heximal firmware of original atmega16u2 microprocessor can be restored;

Reverse AVR Microcomputer ATmega16U2 Flash Program and copy atmel avr mcu atmega16u2 firmware to new microcontroller, the heximal firmware of original atmega16u2 microprocessor can be restored

The ATmega8U2/16U2/32U2 are supported with a full suite of program and system develop- ment tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

AVCC is the supply voltage pin (input) for all analog features (Analog Comparator, PLL). It should be externally connected to VCC through a low-pass filter.

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega8U2/16U2/32U2 as listed on page 74. Port D serves as analog inputs to the analog comparator.

Port D also serves as an 8-bit bi-directional I/O port, if the analog comparator is not used (con- cerns PD2/PD1 pins). Port pins can provide internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in “System Control and Reset” on page 47. Shorter pulses are not guaranteed to generate a reset. This pin alternatively serves as debugWire channel or as generic I/O. The configuration depends on the fuses RST- DISBL and DWEN.

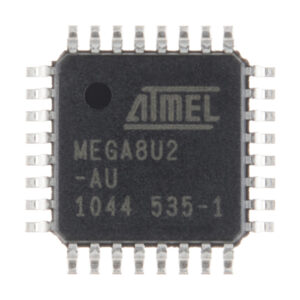

Recover Secured MCU ATmega8U2 Flash Heximal

Recover Secured MCU ATmega8U2 Flash Heximal

Recover Secured MCU ATmega8U2 Flash Heximal after unlock atmega8 microcontroller flash memory protection and extract avr chip atmega8u2 binary code from its flash and eeprom memory;

Recover Secured MCU ATmega8U2 Flash Heximal after unlock atmega8 microcontroller flash memory protection and extract avr chip atmega8u2 binary code from its flash and eeprom memory

The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping when pulling flash content of microchip atmega8u2 mcu memory. This allows very fast start-up combined with low power consumption. In Extended Standby mode, the main Oscillator continues to run.

The device is manufactured using Atmel’s high-density nonvolatile memory technology. The on- chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an on-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory when restoring atmega8l microcomputer flash data. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8U2/16U2/32U2 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

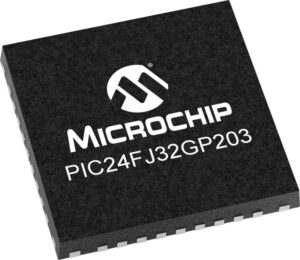

Microchip PIC24FJ32GP203 MCU Flash Memory Heximal Restoration

Microchip PIC24FJ32GP203 MCU Flash Memory Heximal Restoration

Microchip PIC24FJ32GP203 MCU Flash Memory Heximal Restoration including unlocking PIC24FJ32GP203 MCU program memory and extract pic24fj32gp203 secured microcontroller flash memory source code;

Microchip PIC24FJ32GP203 MCU Flash Memory Heximal Restoration including unlocking PIC24FJ32GP203 MCU program memory and extract pic24fj32gp203 secured microcontroller flash memory source code

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost-effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10 μF ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/+80% (Y5V) when breaking pic24fj16ga002 microcontroller flash memory heximal. However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

unlock locked microprocessor PIC24FJ32GP203 memory and readout embedded firmware code from microcontroller chip PIC24FJ32GP203 flash memory

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex: ±15% over a wide temperature range, but consult the manufacturer’s data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of +22%/-82% when recover pic24fj32gp202 mcu flash memory program. Due to the extreme temperature tolerance, a 10 μF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

Recover Secured MCU PIC24FJ32GP202 Flash Program

Recover Secured MCU PIC24FJ32GP202 Flash Program

Recover Secured MCU PIC24FJ32GP202 Flash Program from its memory needs to crack microcontroller pic24fj32gp202 flash memory and extract source code from pic24fj32gp202 microprocessor flash memory;

Recover Secured MCU PIC24FJ32GP202 Flash Program from its memory needs to crack microcontroller pic24fj32gp202 flash memory and extract source code from pic24fj32gp202 microprocessor flash memory

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements.

For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper when executing microcontroller pic24fj16ga002 software decryption. The jumper is replaced for normal run-time operations. Any components associated with the MCLR pin should be placed within 0.25 inch (6 mm) of the pin.

- R1 ≤ 10 kΩ is A suggested starting value is 10 kΩ. Ensure that the MCLR pin VIH and VIL specifications are met.

- R2 ≤ 470Ω will limit any current flowing into MCLR from the external capacitor, C, in the event of a MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met;

A low-ESR (< 5Ω) capacitor is required on the VCAP pin to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must use a capacitor of 10 µF connected to ground to break microcontroller pic24fj16ga002 flash memory heximal program. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

crack secured microcontroller PIC24FJ32GP202 and readout mcu chip PIC24FJ32GP202 flash memory program and eeprom memory data

Designers may use Figure 2-3 to evaluate the ESR equivalence of candidate devices. The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to 27.4 On-Chip Voltage Regulator for additional information.

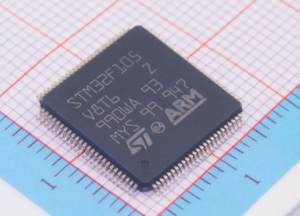

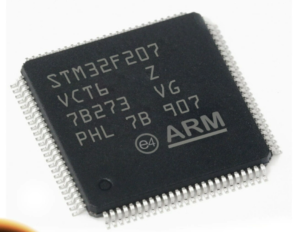

Reverse Secured STM32F207VCT6 Microprocessor Flash Heximal

Reverse Secured STM32F207VCT6 Microprocessor Flash Heximal

Reverse Secured STM32F207VCT6 Microprocessor Flash Heximal and dump embedded firmware from stm32f207vct6 flash memory, extract source code from stm32f207vct6 flash memory;

Reverse Secured STM32F207VCT6 Microprocessor Flash Heximal and dump embedded firmware from stm32f207vct6 flash memory, extract source code from stm32f207vct6 flash memory;

Peripheral available only on STM32F207xx devices.

The STM32F207xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for Ethernet LAN communications through an industry-standard medium- independent interface (MII) or a reduced medium-independent interface (RMII).

The STM32F207xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F207xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) or 50 MHz (RMII) output from the STM32F207xx by restoring stm32f205zct6 locked mcu chip memory content.

obrnuti inženjer osigurao STM32F207VCT6 mikroprocesorski sustav otpora neovlaštenog mijenjanja i program za flash memoriju za očitavanje i softver iz otključanog mikrokontrolera STM32F207VCT6 kopirati ugrađeni firmware izvornog koda na novi STM32F207VCT6 zaštitni MCU čip,

The STM32F207xx includes the following features:

Supports 10 and 100 Mbit/s rates

Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F20x and STM32F21x reference manual for details)

Tagged MAC frame support (VLAN support)

Half-duplex (CSMA/CD) and full-duplex operation

MAC control sublayer (control frames) support

32-bit CRC generation and removal

inżynieria wsteczna zabezpieczony STM32F207VCT6 mikroprocesorowy system odporności na manipulacje oraz odczyt programu pamięci flash i oprogramowania z odblokowanego mikrokontrolera STM32F207VCT6 kopiowania wbudowanego oprogramowania układowego kodu źródłowego do nowego STM32F207VCT6 ochronnego układu MCU,

Several address filtering modes for physical and multicast address (multicast and group addresses)

32-bit status code for each transmitted or received frame

Internal FIFOs to buffer transmit and receive The transmit FIFO and the receive FIFO are both 2 Kbytes (4 Kbytes in total)

Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

Triggers interrupt when system time becomes greater than target time