Break Locked ATmega32U2 Microprocessor Flash

Break Locked ATmega32U2 Microprocessor Flash

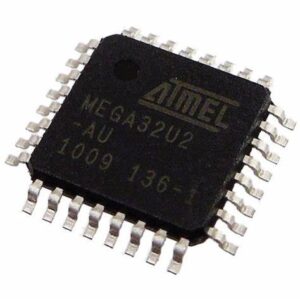

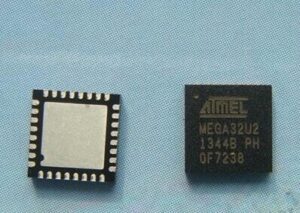

Break Locked ATmega32U2 Microprocessor Flash and copy heximal firmware to new atmega32u2 flash memory and eeprom memory, the source code of binary program and data will be pull out from original master mcu atmega32u2;

Break Locked ATmega32U2 Microprocessor Flash and copy heximal firmware to new atmega32u2 flash memory and eeprom memory, the source code of binary program and data will be pull out from original master mcu atmega32u2

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. Output from the inverting Oscillator amplifier if enabled by Fuse. Also serves as a generic I/O. This documentation contains simple code examples that briefly show how to use various parts of the device. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documen- tation for more details.

These code examples assume that the part specific header file is included before compilation. For I/O registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

reverse engineering ATMEGA32U2 secured mcu fuse bit and dump firmware binary or heximal out of ATMEGA32U2 flas memory

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories when reversing atmega16u2 microcontroller protection, perform calculations, control peripherals, and handle interrupts.

Break Locked ATmega32U2 Microprocesador Flash y copie el firmware heximal a la nueva memoria flash atmega32u2 y memoria eeprom, el código fuente del programa binario y los datos se extraerán del mcu maestro original atmega32u2

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is prefetched from the program memory after recovering atmega8u2 encrypted microprocessor flash memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.