Break Chip ATmega1284V Code

Break Chip ATmega1284V Code

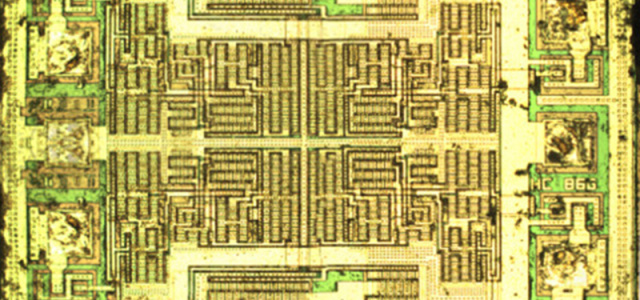

Break Chip ATmega1284V security fuse bit by crack MCU ATmega1284V tamper resistance system, extract Microcontroller code from flash memory and eeprom memory;

Break Chip ATmega1284V security fuse bit by crack MCU ATmega1284V tamper resistance system, extract Microcontroller code from flash memory and eeprom memory

Many register and bit references in this section are written in general form. A lower case “n” replaces the Timer/Counter number, in this case 0. A lower case “x” replaces the Output Compare Unit, in this case Compare Unit A or Compare Unit B.

However, when using the register or bit defines in a program, the precise form must be used, i.e., TCNT0 for accessing Timer/Counter0 counter value and so on. The definitions in Table 69 are also used extensively throughout the document. The Timer/Counter can be clocked by an internal or an external clock source before chip PIC16F72A binary recovery.

The clock source is selected by the Clock Select logic which is controlled by the Clock Select (CS02:0) bits located in the Timer/Counter Control Register (TCCR0B), the main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 39 shows a block diagram of the counter and its surroundings when recover IC PIC16F687 software.

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock (clkT0). ClkT0 can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of whether clkT0 is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM01 and WGM00 bits located in the Timer/Counter Control Register (TCCR0A) and the WGM02 bit located in the Timer/Counter Control Register B (TCCR0B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC0A and OC0B. The Timer/Counter Overflow Flag (TOV0) is set according to the mode of operation selected by the WGM02:0 bits. TOV0 can be used for generating a CPU interrupt.

Break IC ATmega1284 Firmware

Break IC ATmega1284 Firmware

Break IC ATmega1284 protective system and unlock mcu atmega1284 embedded flash memory, and embedded firmware will be readout from microcontroller atmega1284;

All AVR ports have true Break-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions when recover microcontroller stm32f105rct6 bin.

The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. The pin driver is strong enough to drive LED displays directly.

All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both VCC and Ground as indicated in Figure 33. Refer to “Electrical Characteristics” on page 367 for a complete list of parameters before break freescale mcu mc9s12xdg128.

All registers and bit references in this section are written in general form. A lower case “x” represents the numbering letter for the port, and a lower case “n” represents the bit number. However, when using the register or bit defines in a program, the precise form must be used.

For example, PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in “Register Description for I/O-Ports” on page 112 if break microcontroller atmega128 hex.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is break only, while the Data Register and the Data Direction Register are break/write. However, writing a logic one to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register.

In addition, the Pull-up Disable – PUD bit in MCUCR disables the pull-up function for all pins in all ports when set. Using the I/O port as General Digital I/O is described in “Ports as General Digital I/O” on page 82. Most port pins are multiplexed with alternate functions for the peripheral features on the device.

How each alternate function interferes with the port pin is described in “Alternate Port Functions” on page 86. Refer to the individual module sections for a full description of the alternate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O. The ports are bi-directional I/O ports with optional internal pull-ups. Figure 34 shows a functional description of one I/O-port pin, here generically called Pxn.

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in “Register Description for I/O-Ports” on page 112, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

Attack MCU PIC16C558 Program

Attack MCU PIC16C558 Program

Attack MCU PIC16C558 secured system by disable the security fuse bit embedded in the microcontroller PIC16C558 , extract microprocessor program and data from flash memory;

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized when Attack MCU. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available after breaking MCU PIC10F200 program.

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential. The high performance of the PIC16C55X(A) family can be attributed to a number of architectural features commonly found in RISC microprocessors.

To begin with, the PIC16C55X(A) uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses after Attack MCU. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions.

A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C554(A) addresses 512 x 14 on-chip program memory. The PIC16C556A addresses 1K x 14 program memory. The PIC16C558(A) addresses 2K x 14 program memory. All program memory is internal. The PIC16C55X(A) can directly or indirectly address its register files or data memory when unlock microprocessor pic16c558 protective system and extract firmware from flash and eeprom memory.

All special function registers including the program counter are mapped into the data memory. The PIC16C55X(A) have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode after Attack MCU TMS320F241PG heximal. This symmetrical nature and lack of ‘special optimal situations’ make programming with the PIC16C55X(A) simple yet efficient. In addition, the learning curve is reduced significantly.

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

Attack MCU AT91SAM7S256 Binary

Attack MCU AT91SAM7S256 Binary

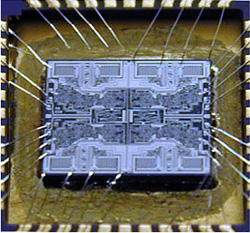

Attack MCU AT91SAM7S256 and break microcontroller at91sam7s256 fuse bit, extract embeded Binary from ATMEL microprocessor flash and eeprom memory;

· Incorporates the ARM7TDMI® ARM® Thumb® Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

– Leader in MIPS/Watt

– Embedded*ICE™ In-circuit Emulation, Debug Communication Channel Support

Internal High-speed Flash

– 256 kbytes, organized in 1024 Pages of 256 Bytes (AT91SAM7S256)

– 128 kbytes, organized in 512 Pages of 256 Bytes (AT91SAM7S128)

– 64 kbytes, organized in 512 Pages of 128 Bytes (AT91SAM7S64)

– 32 kbytes, organized in 256 Pages of 128 Bytes (AT91SAM7S321/32)

– Single Cycle Access at Up to 30 MHz in Worst Case Conditions

– Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed after break avr atmega64a MCU

– Page Programming Time: 6 ms, Including Page Auto-erase, Full Erase Time: 15 ms

– 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities,

Flash Security Bit

– Fast Flash Programming Interface for High Volume Production

Internal High-speed SRAM, Single-cycle Access at Maximum Speed

– 64 kbytes (AT91SAM7S256)

– 32 kbytes (AT91SAM7S128)

– 16 kbytes (AT91SAM7S64)

– 8 kbytes (AT91SAM7S321/32)

Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

Reset Controller (RSTC)

– Based on Power-on Reset and Low-power Factory-calibrated Brown-out Detector

– Provides External Reset Signal Shaping and Reset Source Status

Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

Power Management Controller (PMC)

– Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode

– Three Programmable External Clock Signals

Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention by break microcontroller atmega128 hex

Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signals to the System

– Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

Eleven (AT91SAM7S256/128/64/321) or Nine (AT91SAM7S32) Peripheral DMA Controller (PDC) Channels

One USB 2.0 Full Speed (12 Mbits per Second) Device Port (Except for the AT91SAM7S32).

– On-chip Transceiver, 328-byte Configurable Integrated FIFOs

One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

Two (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Manchester Encoder/Decoder (AT91SAM7S256/128)

– Full Modem Line Support on USART1 (AT91SAM7S256/128/64/321)

One Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

One Three (AT91SAM7S256/128/64/321)-channel or Two (AT91SAM7S32)-channel 16-bit Timer/Counter (TC)

– Three (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) External Clock Inputs, Two Multi-purpose I/O Pins per Channel before Attack MCU

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

One Four-channel 16-bit PWM Controller (PWMC)

One Two-wire Interface (TWI)

– Master Mode Support Only, All Two-wire Atmel EEPROMs Supported

One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

SAM-BA™ Boot Assistant

– Default Boot program

– Interface with SAM-BA Graphic User Interface

IEEE 1149.1 JTAG Boundary Scan on All Digital Pins if Attack MCU

5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each

Power Supplies

– Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

– 3.3V or 1.8V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

– 1.8V VDDCORE Core Power Supply with Brown-out Detector

Fully Static Operation: Up to 55 MHz at 1.65V and 85° C Worst Case Conditions

Available in a 64-lead LQFP Green Package (AT91SAM7S256/128/64/321) and 48-lead LQFP Green Package (AT91SAM7S32).

Recover MCU PIC16C63A Software

Recover MCU PIC16C63A Software

Recover MCU PIC16C63A software from Microcontroller PIC16C63A flash memory, the status of microprocessor PIC16C63A can be reset from locked to unlocked one by MCU cracking technology;

PIC16CXX Microcontroller Core Features:

· High performance RISC CPU

· Only 35 single word instructions to learn

· All single cycle instructions except for program branches which are two cycle

· Operating speed: DC – 20 MHz clock input DC – 200 ns instruction cycle

· 4 K x 14 words of Program Memory, 192 x 8 bytes of Data Memory (RAM)

· Interrupt capability

· Eight-level deep hardware stack

· Direct, indirect and relative addressing modes

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Programmable code protection against mcu pic16c63a memory data unlocking

· Power-saving SLEEP mode crystal/clock

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Capture, Compare, PWM modules

– Capture is 16-bit, max. resolution is 200 ns

– Compare is 16-bit, max. resolution is 200 ns

– PWM max. resolution is 10-bit

· 8-bit multichannel Analog-to-Digital converter

· Synchronous Serial Port (SSP) with SPITM and I2CTM

· Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

· Parallel Slave Port (PSP), 8-bits wide with external RD, WR and CS controls

· Brown-out detection circuitry for Brown-out Reset (BOR)

· Selectable oscillator options

· Low power, high speed CMOS EPROM technology

· Wide operating voltage range: 2.5V to 5.5V

· High Sink/Source Current 25/25 mA

· Commercial, Industrial and Automotive temperature ranges

· Low power consumption:

– < 5 mA @ 5V, 4 MHz

– 23 µA typical @ 3V, 32 kHz

– < 1.2 µA typical standby current

Recover IC PIC16C73B Firmware

Recover IC PIC16C73B Firmware

Recover IC PIC16C73B Firmware from MCU PIC16C73B flash memory, reset the status of microcontroller from locked to open by crack Microcontroller security fuse bit;

A highly reliable Watchdog Timer (WDT), with its own on-ic RC oscillator, provides protection against software lockup, and also provides one way of waking the device from SLEEP.

A UV erasable CERDIP packaged version is ideal for code development, while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C73B devices fit nicely in many applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient after Crack mcu pic16c73b flash and eeprom memory, readout embedded program/data from them.

The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C65B devices very versatile, even in areas where no microcontroller use has been considered before (e.g., timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

PICmicrochip® devices are supported by the complete line of Microchip Development tools. Please refer to Section 15.0 for more details about Microchip’s development tools.

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C63A/65B/73B/74B Product Identification System section at the end of this data sheet when Reading mcu pic16c73b eeprom memory content. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C7X family, there are two device “types” as indicated in the device number.

Copy Microcontroller PIC16C771 Firmware

Copy Microcontroller PIC16C771 Firmware

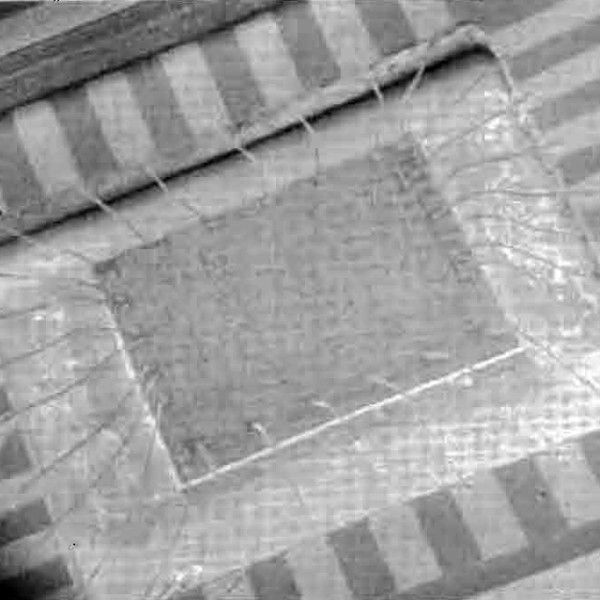

Copy Microcontroller PIC16C771 Firmware which include the program of flash memory and data of eeprom memory, disable the security fuse bit by focus MCU cracking ion beam technique, extract code from MCU PIC16C771 memory;

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the microcontrollere. These registers are implemented as microcontroller RAM.

core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section. For example, CLRF STATUS will clear the upper-three when breaking microcontroller TMS320F28044 heximal;

The STATUS register, shown in Register 2-1, contains the arithmet microcontroller status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the microcontroller log microcontroller. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the ”Instruction Set Summary. when break microcontroller PIC16F886 software

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register occur through the PCLATH register.

PMICROCONTROLLER16C717/770/771 microcontrolleres are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program

memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed.

A return instruction pops a PC address off the stack onto the PC register. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions ( POPs the address from the stack).

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution. Mid-range microcontroller have an 8-level deep x 13-bit wide hardware stack.

The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is Pushed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is Poped in the event of RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

The INDF register is not a microcontroller register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1 Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the microcontroller. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin which normally executed for cracking microcontroller pic16c771 fuse bit.

Additional information on I/O ports may be found in the microcontroller Mid-Range Reference Manual, (DS33023).

PORTA is a 8-bit wide bi-directional port. The corre-analog mode of the corresponding pins. sponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pins RA<3:0> are multiplexed with analog functions, such as analog inputs to the A/D converter, analog VREF inputs, and the on-board band gap reference outputs. When the analog peripherals are using any of Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output.

Pin RA5 is multiplexed with the microcontroller reset (MCLR) and programming input (VPP) functions. The RA5/ MCLR/VPP input only pin has a Schmitt Trigger input buffer. All other RA port pins have Schmitt Trigger input buffers and full CMOS output buffers. Pins RA6 and RA7 are multiplexed with the oscillator input and output functions. The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

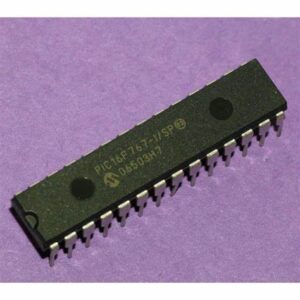

Break Microcontroller PIC16F767 Firmware

Break Microcontroller PIC16F767 Firmware

Break Microcontroller PIC16F767 protected memory include flash and eeprom area, readout embedded firmware from MCU PIC16F767 memory in the format of heximal and recover the file to blank MCU PIC16F767

Break Microcontroller PIC16F767 protected memory include flash and eeprom area, readout embedded firmware from MCU PIC16F767 memory in the format of heximal and recover the file to blank MCU PIC16F767;

Low-Power Features:

· Power-Managed modes:

– Primary Run (XT, RC oscillator, 76 µA,

1 MHz, 2V)

– RC_RUN (7 µA, 31.25 kHz, 2V)

– SEC_RUN (9 µA, 32 kHz, 2V)

– Sleep (0.1 µA, 2V)

· Timer1 Oscillator (1.8 µA, 32 kHz, 2V)

· Watchdog Timer (0.7 µA, 2V)

· Two-Speed Oscillator Start-up Oscillators:

· Three Crystal modes: – LP, XT, HS (up to 20 MHz)

· Two External RC modes

· One External Clock mode: – ECIO (up to 20 MHz)

· Internal Oscillator Block:

– 8 user-selectable frequencies (31 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz, 8 MHz)

Analog Features:

· 10-bit, up to 14-channel Analog-to-Digital Converter

– Programmable Acquisition Time

– Conversion available during Sleep mode

· Dual Analog Comparators

· Programmable Low-Current Brown-out Reset (BOR) Circuitry and Programmable Low-Voltage Detect (LVD)

Peripheral Features:

· High Sink/Source Current: 25 mA

· Two 8-bit Timers with Prescaler

· Timer1/RTC module:

– 16-bit timer/counter with prescaler

– Can be incremented during Sleep via external 32 kHz watch crystal

· Master Synchronous Serial Port (MSSP) with 3-wire SPITM and I2CTM (Master and Slave) modes

· Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART)

· Three Capture, Compare, PWM modules:

– Capture is 16-bit, max. resolution is 12.5 ns

– Compare is 16-bit, max. resolution is 200 ns

– PWM max. resolution is 10 bits

· Parallel Slave Port (PSP) – 40/44-pin devices only

Special Microcontroller Features:

· Fail-Safe Clock Monitor for protecting critical applications against crystal failure

· Two-Speed Start-up mode for immediate code execution

· Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Programmable Code Protection

· Processor Read Access to Program Memory

· Power-Saving Sleep mode

· In-Circuit Serial Programming (ICSP) via two pins

· MPLAB® In-Circuit Debug (ICD) via two pins

· MCLR pin function replaceable with input only pin

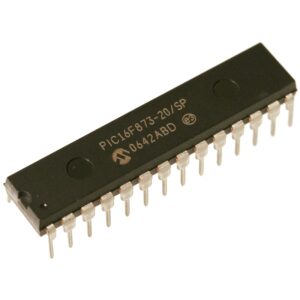

Recover IC PIC16F873 Heximal

Recover IC PIC16F873 Heximal

Recover IC PIC16F873 Heximal out from Microcontroller PIC16F873 secured memory, remove the protection over MCU PIC16F873 by Unlocking microcontroller security fuse bit, and readout the firmware from MCU flash memory;

Devices Included in this Data Sheet:

Analog Features:

· 10-bit, up to 8-channel Analog-to-Digital Converter (A/D)

· Brown-out Reset (BOR)

High-Performance RISC CPU:

· Only 35 single-word instructions to learn

· All single-cycle instructions except for program branches, which are two-cycle

· Operating speed: DC – 20 MHz clock input DC – 200 ns instruction cycle

· Up to 8K x 14 words of Flash Program Memory,

Up to 368 x 8 bytes of Data Memory (RAM),

Up to 256 x 8 bytes of EEPROM Data Memory

· Pinout compatible to other 28-pin or 40/44-pin PIC16CXXX and PIC16FXXX microcontrollers

Peripheral Features:

· Timer0: 8-bit timer/counter with 8-bit prescaler

· Timer1: 16-bit timer/counter with prescaler, can be incremented during Sleep via external crystal/clock

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Two Capture, Compare, PWM modules

– Capture is 16-bit, max. resolution is 12.5 ns

– Compare is 16-bit, max. resolution is 200 ns

– PWM max. resolution is 10-bit

· Synchronous Serial Port (SSP) with SPI™ (Master mode) and I2C™ (Master/Slave)

· Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9-bit address detection

· Parallel Slave Port (PSP) – 8 bits wide with external RD, WR and CS controls (40/44-pin only)

· Brown-out detection circuitry for Brown-out Reset (BOR)

· Analog Comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (VREF) module

– Programmable input multiplexing from device inputs and internal voltage reference

– Comparator outputs are externally accessible

Special Microcontroller Features:

· 100,000 erase/write cycle Enhanced Flash program memory typical

· 1,000,000 erase/write cycle Data EEPROM memory typical

· Data EEPROM Retention > 40 years

· Self-reprogrammable under software control

· In-Circuit Serial Programming™ (ICSP™) via two pins

· Single-supply 5V In-Circuit Serial Programming

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Programmable code protection

· Power saving Sleep mode

· Selectable oscillator options

· In-Circuit Debug (ICD) via two pins CMOS Technology:

· Low-power, high-speed Flash/EEPROM technology

· Fully static design

· Wide operating voltage range (2.0V to 5.5V)

· Commercial and Industrial temperature ranges

· Low-power consumption

Copy MCU PIC18F4685 Software

Copy MCU PIC18F4685 Software

Copy MCU PIC18F4685 software inside microcontroller PIC18F4685 flash memory, decapsulate silicon package of microcontroller and get its fuse bit exposed, so MCU cracking technique will be able to reset the bit and readout the firmware from Microcontroller;

Power-Managed Modes:

Peripheral Highlights:

Run: CPU on, peripherals on

Idle: CPU off, peripherals on

Sleep: CPU off, peripherals off

Idle mode currents down to 5.8 ìA typical

Sleep mode currents down to 0.1 ìA typical

Timer1 Oscillator: 1.1 ìA, 32 kHz, 2V

Watchdog Timer: 2.1 ìA

Two-Speed Oscillator Start-up

unlock encrypted mcu pic18f4685 fuse and copy firmware program file as heximal to new microcontroller

High-Current Sink/source 25 mA/25 mA

Three External Interrupts

One Capture/Compare/PWM (CCP1) module

Enhanced Capture/Compare/PWM (ECCP1) module

(40/44-pin devices only):

– One, two or four PWM outputs

– Selectable polarity

– Programmable dead time

Flexible Oscillator Structure:

· Four Crystal modes, up to 40 MHz

· 4x Phase Lock Loop (PLL) – available for crystal and internal oscillators

· Two External RC modes, up to 4 MHz

· Two External Clock modes, up to 40 MHz

· Internal Oscillator Block:

– 8 user-selectable frequencies, from 31 kHz to 8 MHz

– Provides a complete range of clock speeds,

from 31 kHz to 32 MHz when used with PLL

– User-tunable to compensate for frequency drift

· Secondary Oscillator using Timer1 @ 32 kHz

· Fail-Safe Clock Monitor

– Allows for safe shutdown if peripheral clock stops

– Auto-shutdown and auto-restart

Master Synchronous Serial Port (MSSP) module supporting 3-Wire SPI (all 4 modes) and I2C™

Master and Slave modes

Enhanced Addressable USART module:

– Supports RS-485, RS-232 and LIN 1.3

– RS-232 operation using internal oscillator block (no external crystal required)

– Auto-wake-up on Start bit

– Auto-Baud Detect

10-Bit, up to 11-Channel Analog-to-Digital

Converter module (A/D), up to 100 ksps:

– Auto-acquisition capability

– Conversion available during Sleep

Dual Analog Comparators with Input Multiplexing

Special Microcontroller Features:

· C compiler Optimized Architecture with optional

Extended Instruction Set

· 100,000 Erase/Write Cycle Enhanced Flash

Program Memory typical

· 1,000,000 Erase/Write Cycle Data EEPROM

Memory typical

· Flash/Data EEPROM Retention: > 40 years

· Self-Programmable under Software Control

· Priority Levels for Interrupts

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 41 ms to 131s

· Single-Supply 5V In-Circuit Serial

Programming™ (ICSP™) via two pins

· In-Circuit Debug (ICD) via two pins

· Wide operating voltage range: 2.0V to 5.5V

ECAN Module Features:

· Message bit rates up to 1 Mbps

· Conforms to CAN 2.0B ACTIVE Specification

· Fully Backward Compatible with PIC18XXX8 CAN modules

· Three Modes of Operation:

– Legacy, Enhanced Legacy, FIFO

· Three Dedicated Transmit Buffers with Prioritization

· Two Dedicated Receive Buffers

· Six Programmable Receive/Transmit Buffers

· Three Full, 29-Bit Acceptance Masks

· 16 Full, 29-Bit Acceptance Filters w/Dynamic Association

· DeviceNet™ Data Byte Filter Support

· Automatic Remote Frame Handling

· Advanced Error Management Features