Archive for the ‘Break IC’ Category

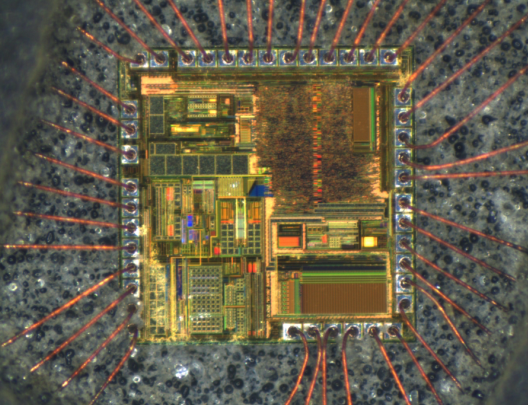

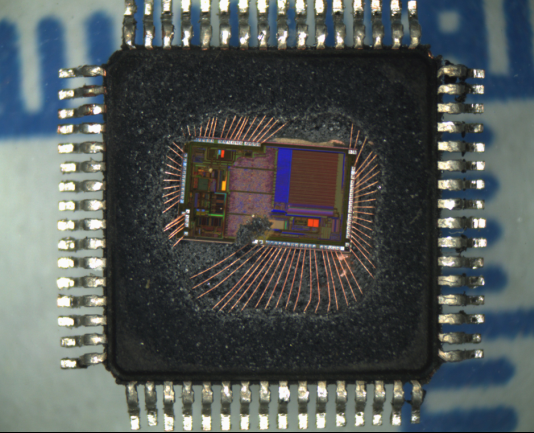

Attack ATMEGA32U2-MU Microprocessor Fuse Bit

Attack ATMEGA32U2-MU Microprocessor Fuse Bit

Attack ATMEGA32U2-MU Microprocessor Fuse Bit and unlock secured atmega32u2 processor protection over its embedded flash memory heximal, and then extract source code from atmega32u2 mcu;

The period of the Watchdog Oscillator is 1 µs (nominal) at 5.0V and 25°C. The frequency of the Watchdog Oscillator is voltage dependent as shown in “Electrical Characteristics – TA = -40°C to 85°C” on page 232.

The MCU will wake up if the input has the required level during this sampling or if it is held until the end of the start-up time. The start-up time is defined by the SUT Fuses as described in “System Clockand Clock Options” on page 31.

If the level is sampled twice by the Watchdog Oscillator clock but disappears before the end of the start-up time, the MCU will still wake up, but no interrupt will be generated to recover atmega32 mcu flash program and eeprom data. The required level must be held long enough for the MCU to complete the wake up to trigger the level interrupt.

Attack ATMEGA32U2-MU Microprocessor Fuse Bit and unlock secured atmega32u2 processor protection over its embedded flash memory heximal, and then extract source code from atmega32u2 mcu

The MCU Control Register contains control bits for interrupt sense control and general MCU functions. The External Interrupt 1 is activated by the external pin INT1 if the SREG I-bit and the corresponding interrupt mask in the GICR are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 14-1.

The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt when restoring atmega32l microprocessor memory software. Shorter pulses are not guaranteed to gener- ate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

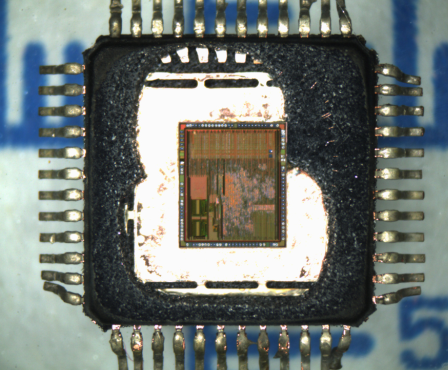

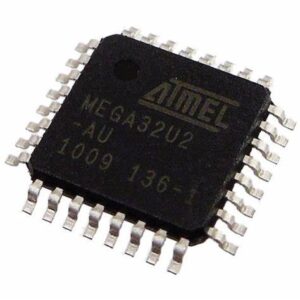

Break ATMEGA32U2-AU Microcontroller Flash Memory

Break ATMEGA32U2-AU Microcontroller Flash Memory

Break ATMEGA32U2-AU Microcontroller Flash Memory and clone microprocessor memory data to new atmega32u2 chip, the embedded software will be readout from mcu atmega32u2;

This is set up as indicated in the specification for the MCU Control Register – MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

Note that recognition of falling or rising edge interrupts on INT0 and INT1 requires the presence of an I/O clock when reverse engineering atmel avr chip atmega32a program file, described in “Clock Systems and their Distribution”.

Low level interrupts on INT0/INT1 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

quebrar ATMEGA32U2-AU microcontrolador de memória flash e clonar dados de memória de microprocessador para o novo chip atmega32u2, o software incorporado será lido a partir de mcu atmega32u2

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU in the process of recover protected atmega32 mcu memory. This makes the MCU less sensitive to noise. The changed level is sampled twice by the Watchdog Oscillator clock.

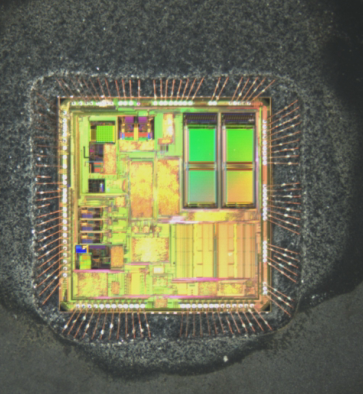

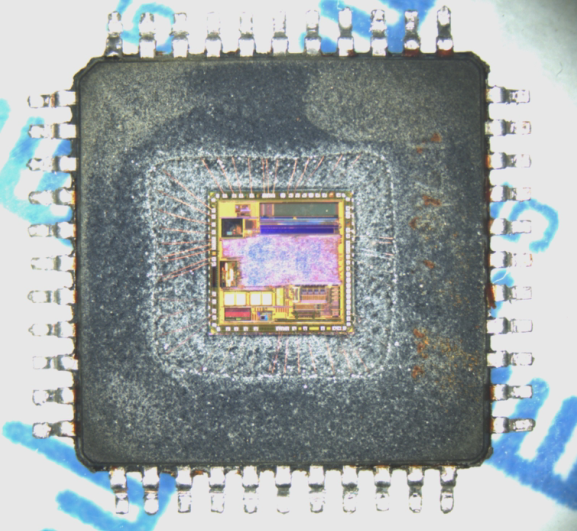

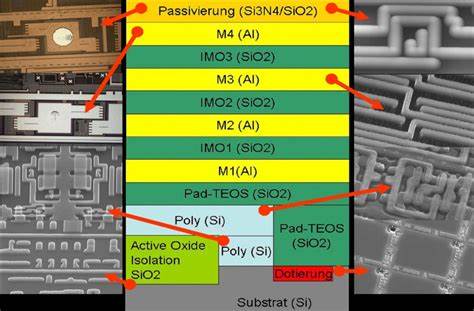

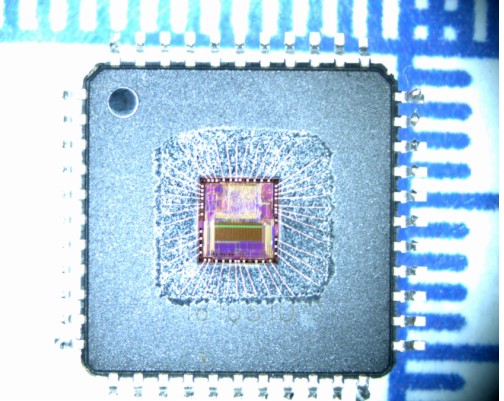

Decap Microchip PIC18F1320 Processor

Decap Microchip PIC18F1320 Processor

Decap Microchip PIC18F1320 Processor and then extract flash and eeprom memory content from pic18f1320 mcu chip, the source code will be copied embedded firmware from pic18f1320 microcontroller flash memory,

All of the devices in the PIC18F1220/1320 family offer nine different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

Four Crystal modes, using crystals or ceramic resonators.

Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output), or one pin (oscillator input, with the second pin reassigned as general I/O).

Two External RC Oscillator modes, with the same pin options as the External Clock modes.

An internal oscillator block, which provides an 8 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of six user-selectable clock frequencies (from 125 kHz to 4 MHz) for a total of 8 clock frequencies.

decap Microchip PIC18F1320 processador e, em seguida, extrair flash e eeprom conteúdo de memória de pic18f1320 mcu chip, o código-fonte será copiado firmware incorporado da memória flash do microcontrolador pic18f1320,

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs by recovering pic18f1330 microchip mcu source code, the controller is switched to the internal oscillator block, allowing for continued low-speed operation, or a safe application shutdown.

Two-Speed Start-up: This option allows the internal oscillator to serve as the clock source from Power- on Reset, or wake-up from Sleep mode, until the primary clock source is available in the process of attacking pic18f13k50 microcontroller flash memory. This allows for code execution during what would otherwise be the clock start-up interval and can even allow an application to perform routine background activities and return to Sleep without returning to full-power operation.

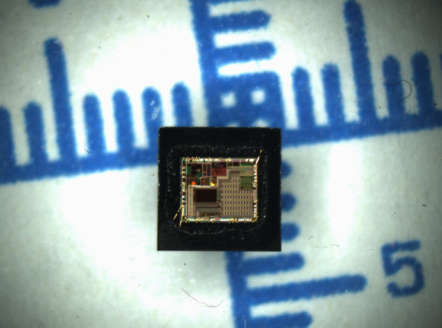

Decode Secured PIC18F1220 Microcontroller Program

Decode Secured PIC18F1220 Microcontroller Program

Decode Secured PIC18F1220 Microcontroller Program from its flash and eeprom memory, copy the firmware to new mcu pic18f1220 which will perform the same functions, original source code in the format of heximal will be extracted from processor pic18f1220;

This family offers the advantages of all PIC18 microcon- trollers – namely, high computational performance at an economical price – with the addition of high endurance Enhanced Flash program memory.

On top of these fea- tures, the PIC18F1220/1320 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications when reverse engineering pic18f2580 microprocessor embedded software.

decodificar o programa microcontrolador PIC18F1220 protegido de sua memória flash e eeprom, copiar o firmware para o novo mcu pic18f1220 que executará as mesmas funções, o código-fonte original no formato de heximal será extraído do processador pic18f1220

All of the devices in the PIC18F1220/1320 family incor- porate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled, but the peripherals are still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements by recover pic18f2553 mcu flash heximal.

- On-the-fly Mode Switching: The power managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application’s software design.

- Lower Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer have been reduced by up to 80%, with typical values of 1.1 and 2.1 mA, respectively.

Decrypt Microcontroller ATMEGA64A Memory Data

Decrypt Microcontroller ATMEGA64A Memory Data

Decrypt Microcontroller ATMEGA64A Memory Data is a process to recover avr atmega64a mcu embedded firmware and readout heximal file from processor atmega64a;

When switching between tri-state ({DDxn, PORTxn} = 0b00) and output high ({DDxn, PORTxn} = 0b11), an inter- mediate state with either pull-up enabled ({DDxn, PORTxn} = 0b01) or output low ({DDxn, PORTxn} = 0b10) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the

difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports when recover protected atmega32 mcu eeprom memory.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ({DDxn, PORTxn} = 0b00) or the output high state ({DDxn, PORTxn} = 0b11) as an intermediate step.

descriptografar microcontrolador ATMEGA64A dados de memória é um processo para recuperar avr atmega64a mcu firmware embutido e arquivo heximal de leitura do processador atmega64a

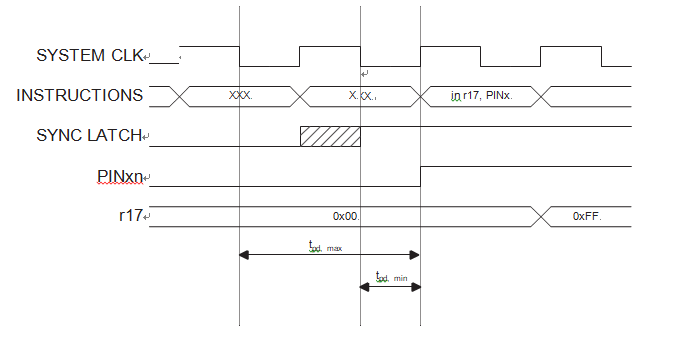

Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register Bit. As shown in Figure 13-2, the PINxn Register bit and the preceding latch constitute a synchronizer by restoring atmega32l microprocessor memory software. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay.

Below Figure shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted tpd,max and tpd,min, respectively.

Break ATMEGA64L Secured Microcontroller Flash Memory

Break ATMEGA64L Secured Microcontroller Flash Memory

Break ATMEGA64L Secured Microcontroller Flash Memory and clone the avr mcu atmega64l heximal content to new MCU, read the firmware program out from atmega64l microprocessor flash and eeprom memory;

Each port pin consists of 3 Register bits: DDxn, PORTxn, and PINxn. As shown in “Register Description” on page 69, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin when recover protective microprocessor atmega16 firmware. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin.

quebrar ATMEGA64L memória flash microcontrolador seguro e clonar o avr mcu atmega64l conteúdo heximal para novo MCU, ler o programa de firmware para fora do atmega64l microprocessador flash e memória eeprom

The port pins are tri-stated when a reset condition becomes active, even if no clocks are running. If PORTxn is written logic one when the pin is configured as an output pin to break atmega16l locked mcu flash memory, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

Break R5F21258SNFP MCU Flash Memory Locking

Break R5F21258SNFP MCU Flash Memory Locking

Break R5F21258SNFP MCU Flash Memory Locking and clone renesas r5f21258sn flash memory content from original chip, extract microprocessor embedded firmware from its flash memory.

R5F21258SNFP has an On-chip Brown-out Detection (BOD) circuit for monitoring the VCC level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the fuse BODLEVEL to be

2.7V (BODLEVEL unprogrammed), or 4.0V (BODLEVEL programmed). The trigger level has a hysteresis to ensure spike free Brown-out Detection when copy r5f212aasd locked flash memory data. The hysteresis on the detection level should be interpreted as VBOT+ = VBOT

+ VHYST/2 and VBOT- = VBOT – VHYST/2.

The BOD circuit can be enabled/disabled by the fuse BODEN. When the BOD is enabled (BODEN programmed), and VCC decreases to a value below the trigger level (VBOT- in Figure 11-5), the Brown-out Reset is immediately activated after reverse engineering r5f21226df microprocessor binary code. When VCC increases above the trigger level (VBOT+ in Figure 11-5), the delay counter starts the MCU after the time-out period tTOUT has expired. The BOD circuit will only detect a drop in VCC if the voltage stays below the trigger level for longer than tBOD given in Table 26-3 on page 235.

Break R8C R5F21336TNFP MCU Flash Program

Break R8C R5F21336TNFP MCU Flash Program

Break R8C R5F21336TNFP MCU Flash Program is a process of cracking renesas microprocessor r5f21336tn flash memory fuse bit, and extract embedded binary file from microcontroller;

There are several issues to consider when trying to minimize the power consumption in an AVR controlled system. In general, sleep modes should be used as much as possible, and the sleep mode should be selected so that as few as possible of the device’s functions are operating.

All functions not needed should be disabled. In particular, the following modules may need special consideration when trying to achieve the lowest possible power consumption in the process of breaking r5f21292sd locked MCU flash memory.

quebrar R8C R5F21336TNFP MCU programa flash é um processo de quebra de microprocessador renesas r5f21336tn memória flash fusível bit, e extrair arquivo binário incorporado do microcontrolador;

If enabled, the ADC will be enabled in all sleep modes. To save power, the ADC should be disabled before entering any sleep mode by attacking renesas r5f21244sd microcontroller protection. When the ADC is turned off and on again, the next conversion will be an extended conversion. Refer to “Analog-to-Digital Converter” on page 189 for details on ADC operation.

When entering Idle mode, the Analog Comparator should be disabled if not used. When entering ADC Noise Reduction mode, the Analog Comparator should be disabled. In the other sleep modes, the Analog Comparator is automatically disabled.

Breaking Encrypted ATMEGA32A MCU Flash

Breaking Encrypted ATMEGA32A MCU Flash

Breaking Encrypted ATMEGA32A MCU Flash and pull microcontroller atmega32a firmware out from its flash and eeprom memory, the software file of atmega32a atmel chip can be readout directly by programmer after reset the fuse bit;

EEPROM data corruption can easily be avoided by following this design recommendation: Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD).

If the detection level of the internal BOD does not match the needed detection level, an external low VCC Reset Protection circuit can be used. If a reset occurs while a write operation is in progress of breaking atmega16l locked mcu flash memory, the write operation will be completed provided that the power supply voltage is sufficient.

quebrando o flash criptografado ATMEGA32A MCU e puxar o microcontrolador atmega32a firmware para fora de sua memória flash e eeprom, o arquivo de software do chip atmega32a atmel pode ser lido diretamente pelo programador após a redefinição do bit de fusível;

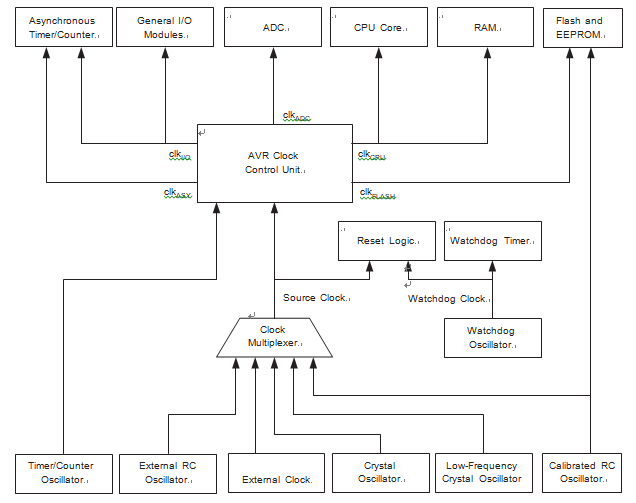

Below Figure presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes, as described in “Power Management and Sleep Modes” on page 39. The clock systems are detailed below Figure.

The CPU clock is routed to parts of the system concerned with operation of the AVR core. Examples of such mod- ules are the General Purpose Register File by recover atmega16 microprocessor firmware, the Status Register and the Data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing general operations and calculations.

Restoring ATmega32L Microprocessor Memory Software

Restoring ATmega32L Microprocessor Memory Software

Restoring ATmega32L Microprocessor Memory Software in the format of heximal or binary, original memory data inside atmega32l mcu will be cloned and embedded firmware will be readout from atmega32l;

The EEPROM Write Enable Signal EEWE is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be written to one to write the value into the EEPROM. The EEMWE bit must be written to one before a logical one is written to EEWE, otherwise no EEPROM write takes place. The following pro- cedure should be followed when writing the EEPROM (the order of steps 3 and 4 is not essential):

- Wait until EEWE becomes zero.

- Wait until SPMEN in SPMCR becomes zero.

- Write new EEPROM address to EEAR (optional).

- Write new EEPROM data to EEDR (optional).

- Write a logical one to the EEMWE bit while writing a zero to EEWE in EECR.

- Within four clock cycles after setting EEMWE, write a logical one to EEWE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write to reverse engineer atmega8a microchip memory. Step 2 is only relevant if the software con- tains a boot loader allowing the CPU to program the Flash.

If the Flash is never being updated by the CPU, step 2 can be omitted. See “Boot Loader Support – Read-While-Write Self-Programming” on page 201 for details about boot programming.

Caution: An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access.

restaurando o software de memória do microprocessador ATmega32L no formato de heximal ou binário, os dados de memória originais dentro do atmega32l mcu serão clonados e o firmware incorporado será lido a partir do atmega32

the EEAR or EEDR Register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems.

When the write access time has elapsed, the EEWE bit is cleared by hardware in order to restore microcontroller atmega8l flash data. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.