Posts Tagged ‘copy microcontroller source binary’

Copy Microcontroller PIC16F767 Program

Copy Microcontroller PIC16F767 Program

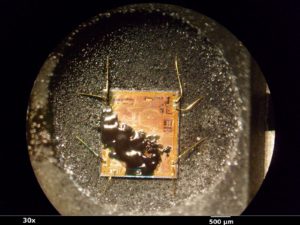

Copy Microcontroller PIC16F767 Program from embedded program memory, protection of mcu pic16f767 will be attacked and copy the new firmware into new MCU pic16f767;

Copy Microcontroller PIC16F767 Program from embedded program memory, protection of mcu pic16f767 will be attacked and copy the new firmware into new MCU pic16f767

MEMORY ORGANIZATION

There are two memory blocks in each of these PICmicro® MCUs. The program memory and data memory have separate buses so that concurrent access can occur and is detailed in this section. The program memory can be read internally by user code (see Section 3.0 “Reading Program Memory”) when copy P87C51X2BBD microcontroller.

Additional information on device memory may be found in the “PICmicro® Mid-Range MCU Family Reference Manual” (DS33023).

The PIC16F767 devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16F767 devices have 8K words of Flash program memory and the PIC16F767 devices have 4K words. The program memory maps for PIC16F7X7 devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound. in the “PICmicro® Mid-Range MCU Family Reference.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits if copy recover 430G2452 microcontroller:

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

Copy Microcontroller PIC16F747 Code

Copy Microcontroller PIC16F747 Code

Copy Microcontroller PIC16F747 Code from embedded flash and eeprom memory, and extract the firmware from MCU pic16f747 memory after crack MCU protection;

Copy Microcontroller PIC16F747 Code from embedded flash and eeprom memory, and extract the firmware from MCU pic16f747 memory after crack MCU protection

Special Microcontroller Features:

· Fail-Safe Clock Monitor for protecting critical applications against crystal failure;

· Two-Speed Start-up mode for immediate code execution

· Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Programmable Code Protection

· Processor Read Access to Program Memory

· Power-Saving Sleep mode

· In-Circuit Serial Programming (ICSP) via two pins

· MPLAB® In-Circuit Debug (ICD) via two pins

· MCLR pin function replaceable with input only pin if Copy chip pic16f870 program

DEVICE OVERVIEW

This document contains device specific information about the following devices:

PIC16F737/767 devices are available only in 28-pin packages, while PIC16F747/777 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X7 family share common architecture with the following differences:

· The PIC16F737 and PIC16F767 have one-half of the total on-chip memory of the PIC16F747 and PIC16F777.

· The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5.

· The 28-pin devices have 16 interrupts, while the 40/44-pin devices have 17.

· The 28-pin devices have 11 A/D input channels, while the 40/44-pin devices have 14.

· The Parallel Slave Port is implemented only on the 40/44-pin devices.

· Low-Power modes: RC_RUN allows the core and peripherals to be clocked from the INTRC, while SEC_RUN allows the core and peripherals to be clocked from the low-power Timer1. Refer to

Section 4.7 “Power-Managed Modes” for further details for the purpose of break pic18f8722 Microcontroller code.

· Internal RC oscillator with eight selectable frequencies, including 31.25 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz and 8 MHz. The INTRC can be configured as a primary or secondary clock source. Refer to Section 4.5 “Internal Oscillator Block” for further details.