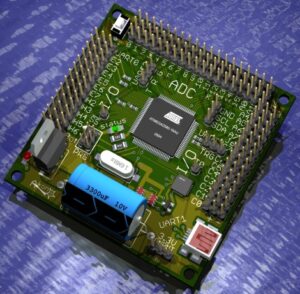

Secured Microchip ATMEGA640V MCU Flash Program Recovery

Secured Microchip ATMEGA640V MCU Flash Program Recovery

Secured Microchip ATMEGA640V MCU Flash Program Recovery needs to firstly crack mcu atmel atmega640v protective system and read atmega640v microcontroller flash memory content out from it;

Secured Microchip ATMEGA640V MCU Flash Program Recovery needs to firstly crack mcu atmel atmega640v protective system and read atmega640v microcontroller flash memory content out from it;

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buf- fers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated to recover atmega640v microcontroller flash firmware. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

microchip seguro atmega640v mcu flash program recovery necesita primero descifrar el sistema de protección mcu atmel atmega640v y leer el contenido de la memoria flash del microcontrolador atmega640v.

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buf- fers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buf- fers have symmetrical drive characteristics with both high sink and source capability after breaking ic chip atmega640v flash protection. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

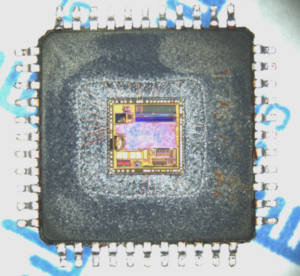

Protected ATMEGA640 MCU Chip Binary Restoration

Protected ATMEGA640 MCU Chip Binary Restoration

Protected ATMEGA640 MCU Chip Binary Restoration is a process to unlock secured microcontroller atmega640 firmware from its flash memory and readout microprocessor atmega640 chipset flash and eeprom software data;

Protected ATMEGA640 MCU Chip Binary Restoration is a process to unlock secured microcontroller atmega640 firmware from its flash memory and readout microprocessor atmega640 chipset flash and eeprom software data;

The device is manufactured using the Microchip high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core.

La restauración binaria del chip ATMEGA640 MCU protegido es un proceso para desbloquear el firmware seguro del microcontrolador atmega640 de su memoria flash y leer los datos del software flash y eeprom del chipset atmega640 del microprocesador;

The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated while reverse engineering atmega640 microcontroller fuse bit, providing true Read- While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the ATmega640v is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega640v AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits. Each device in the ATmega640v family differs only in memory size and number of pins to recover mcu chip atmega640 heximal from flash memory. Table 2-1 summarizes the different configurations for the six devices.

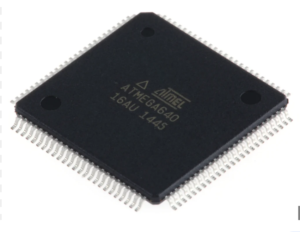

Reverse Protected ATMEGA645 MCU Heximal

Reverse Protected ATMEGA645 MCU Heximal

Reverse Protected ATMEGA645 MCU Heximal is a process to readout chip atmega645 firmware from its flash and eeprom after attack locked microcontroller atmega645 protective system;

Reverse Protected ATMEGA645 MCU Heximal is a process to readout chip atmega645 firmware from its flash and eeprom after attack locked microcontroller atmega645 protective system

Atmel offers the QTouch® library for embedding capacitive touch buttons, sliders and wheels- functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offersrobust sensing and includes fully debounced reporting of touch keys and includes Adjacent KeySuppression® (AKS™) technology for unambiguous detection of key events to copy chip atmega645 mcu file. The easy-to-use QTouch Suite toolchain allows you to explore, develop and debug your own touch applications.

atmega645 mcu protegido inversamente heximal es un proceso para leer el firmware del chip atmega645 desde su flash y eeprom después de un ataque bloqueado sistema de protección del microcontrolador atmega645;

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip In-System re-Programmable (ISP) Flash allows the program memory to be repro- grammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot program can use any interface to download the application program in the Application Flash memory.

Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel Atmel ATmega645 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The Atmel ATmega325/3250/645/6450 is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.

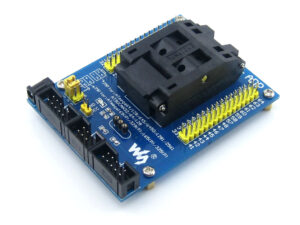

Break Locked Microcontroller ATMEGA645V Flash Memory

Break Locked Microcontroller ATMEGA645V Flash Memory

Break Locked Microcontroller ATMEGA645V Flash Memory will help engineer to recover atmega645v flash embedded heximal, the content inside its flash and eeprom can be readout;

Break Locked Microcontroller ATMEGA645V Flash Memory will help engineer to recover atmega645v flash embedded heximal, the content inside its flash and eeprom can be readout

The Atmel ATmega325/3250/645/6450 provides the following features: 32/64K bytes of In-Sys- tem Programmable Flash with Read-While-Write capabilities, 1/2K bytes EEPROM, 2/4K byte SRAM, 54/69 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes when recover chipset atmega645v heximal file, internal and external interrupts, a serial programmable USART, Universal Serial Interface with Start Condition Detector, an 8-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, an SPI serial port, and five software selectable power saving modes.

romper bloqueado microcontrolador ATMEGA 645Z memoria flash ayudará al ingeniero a recuperar atmega 645v flash incrustado heximal, el contenido dentro de su flash y eeprom se puede leer;

The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer will continue to run, allowing the user to maintain a timer base while the rest of the device is sleeping.

The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC to minimize switching noise during ADC conversions by reverse engineering atmega644a flash firmware. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low- power consumption.

Attack ATmega165PV Microcontroller Flash Memory

Attack ATmega165PV Microcontroller Flash Memory

Attack ATmega165PV Microcontroller Flash Memory and readout atmega165pv secured avr chip flash program, then engineer can extract the source code of locked atmega165pv microprocessor;

Attack ATmega165PV Microcontroller Flash Memory and readout atmega165pv secured avr chip flash program, then engineer can extract the source code of locked atmega165pv microprocessor

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

atacar la memoria flash del microcontrolador ATmega165PV y leer el programa flash de chip avr seguro atmega165pv, luego el ingeniero puede extraer el código fuente del microprocesador atmega165pv bloqueado

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have sym- metrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated to break mcu atmega165 flash memory protection. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

break atmega65pv microcontroller fuse bit and readout embedded heximal file from its flash memory, copy firmware to new original microprocessor atmega165pv

Port G is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated to recover atmega168pv mcu code. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 26-4 on page 302. Shorter pulses are not guaranteed to generate a reset;

Break Microchip ATmega165P Chip Flash Memory

Break Microchip ATmega165P Chip Flash Memory

Break Microchip ATmega165P Chip Flash Memory and extract embedded source code from atmega165p mcu flash memory, which can be viewed as atmega165p microcontroller protection system hacking;

Break Microchip ATmega165P Chip Flash Memory and extract embedded source code from atmega165p mcu flash memory, which can be viewed as atmega165p microcontroller protection system hacking;

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability to copy avr mcu atmega165p memory content. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

rompa la memoria flash del chip Microchip ATmega165P y extraiga el código fuente incrustado de la memoria flash atmega165p mcu, que puede verse como piratería del sistema de protección del microcontrolador atmega165p

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability to break atmega16p flash memory fuse bit. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Reverse Engineer DSP TMS320F28030PAG Microcontroller Flash Memory

Reverse Engineer DSP TMS320F28030PAG Microcontroller Flash Memory

Reverse Engineer DSP TMS320F28030PAG Microcontroller Flash Memory and restore dsp cpu tms320f28030pagt source code, copy flash program to new tms320f28030pag texas instrument dsp mcu;

Reverse Engineer DSP TMS320F28030PAG Microcontroller Flash Memory and restore dsp cpu tms320f28030pagt source code, copy flash program to new tms320f28030pag texas instrument dsp mcu

Section 6.2.1 describes the signals. With the exception of the JTAG pins, the GPIO function is the default at reset, unless otherwise mentioned. The peripheral signals that are listed under them are alternate functions. Some peripheral functions may not be available in all devices. See Table 5-1 for details. Inputs are not 5-V tolerant. All GPIO pins are I/O/Z and have an internal pullup, which can be selectively enabled/disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups on the PWM pins are not enabled at reset. The pullups on other GPIO pins are enabled upon reset. The AIO pins do not have an internal pullup.

memoria flash del microcontrolador DSP TMS320F28030PAG de ingeniería inversa y restauración del código fuente dsp cpu tms320f28030pagt, copia del programa flash al nuevo instrumento tms320f28030pag texas dsp mcu;

When the on-chip VREG is used, the GPIO19, GPIO34, GPIO35, GPIO36, GPIO37, and GPIO38 pins could glitch during power up. This potential glitch will finish before the boot mode pins are read and will not affect boot behavior. If glitching is unacceptable in an application, 1.8 V could be supplied externally.

Alternatively, adding a current-limiting resistor (for example, 470 Ω) in series with these pins and any external driver could be considered to limit the potential for degradation to the pin and/or external circuitry. There is no power-sequencing requirement when using an external 1.8-V supply. However, if the 3.3-V transistors in the level-shifting output buffers of the I/O pins are powered before the 1.8-V transistors, it is possible for the output buffers to turn on, causing a glitch to occur on the pin during power up. To avoid this behavior, power the VDD pins before or with the VDDIO pins, ensuring that the VDD pins have reached 0.7 V before the VDDIO pins reach 0.7 V.

Encrypted ATMEL ATMEGA128A MCU Flash Decoding

Encrypted ATMEL ATMEGA128A MCU Flash Decoding

Encrypted ATMEL ATMEGA128A MCU Flash Decoding will help engineer to copy atmega128a microcontroller flash heximal file out after readout atmega128a microprocessor’s content software from its flash and eeprom memory;

Encrypted ATMEL ATMEGA128A MCU Flash Decoding will help engineer to copy atmega128a microcontroller flash heximal file out after readout atmega128a microprocessor’s content software from its flash and eeprom memory

In this mode, the Watchdog Timer is always enabled, and the WDE bit will always read as one. A timed sequence is needed when changing the Watchdog Time-out period. To change the Watchdog Time-out, the following procedure must be followed:

- In the same operation, write a logical one to WDCE and WDE. Even though the WDE always is set, the WDE must be written to one to start the timed sequence

Within the next four clock cycles, in the same operation, write the WDP bits as desired, but with the WDCE bit cleared. The value written to the WDE bit is irrelevant to break atmega128a mcu fuse bit inside the flash memory.

La decodificación flash MCU ATMEL ATMEGA128A cifrada ayudará al ingeniero a copiar el archivo heximal flash del microcontrolador atmega128a después de leer el software de contenido del microprocesador atmega128a de su memoria flash y eeprom

This section describes the specifics of the interrupt handling performed by the ATmega8. For a general explanation of the AVR interrupt handling, refer to “Reset and Interrupt Handling” on page 14.

Table 19 on page 47 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the boot section or vice versa to break atmega128a ic chip flash memory.

- When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at reset, see “Boot Loader Support – Read-While-Write Self-Programming” on page 202

- When the IVSEL bit in GICR is set, Interrupt Vectors will be moved to the start of the boot Flash The address of each Interrupt Vector will then be the address in this table added to the start address of the boot Flash section;

- The Boot Reset Address is shown in Table 82 on page 213. For the BOOTRST Fuse “1” means unprogrammed while “0” means programmed

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega128A is:

| addressLabels | Code | Comments | ||

| $000 | rjmp | RESET | ; Reset Handler | |

| $001 | rjmp | EXT_INT0 | ; IRQ0 Handler | |

| $002 | rjmp | EXT_INT1 | ; IRQ1 Handler | |

| $003 | rjmp | TIM2_COMP | ; Timer2 Compare Handler | |

| $004 | rjmp | TIM2_OVF | ; Timer2 Overflow Handler | |

| $005 | rjmp | TIM1_CAPT | ; Timer1 Capture Handler | |

| $006 | rjmp | TIM1_COMPA | ; Timer1 CompareA Handler | |

| $007 | rjmp | TIM1_COMPB | ; Timer1 CompareB Handler | |

| $008 | rjmp | TIM1_OVF | ; Timer1 Overflow Handler | |

| $009 | rjmp | TIM0_OVF | ; Timer0 Overflow Handler | |

| $00a | rjmp | SPI_STC | ; SPI Transfer Complete Handler | |

| $00b | rjmp | USART_RXC | ; USART RX Complete Handler | |

| $00c | rjmp | USART_UDRE | ; UDR Empty Handler | |

| $00d | rjmp | USART_TXC | ; USART TX Complete Handler | |

| $00e | rjmp | ADC | ; ADC Conversion Complete Handler | |

| $00f | rjmp | EE_RDY | ; EEPROM Ready Handler | |

| $010 | rjmp | ANA_COMP | ; Analog Comparator Handler | |

| $011 | rjmp | TWSI | ; Two-wire Serial Interface Handler | |

| $012 | rjmp | SPM_RDY | ; Store Program Memory Ready Handler | |

| ; | ||||

| $013 | RESET: ldi | r16,high(RAMEND); Main program start | ||

| $014 | out | SPH,r16 ; Set Stack Pointer to top of RAM | ||

| $015 | ldi | r16,low(RAMEND) | ||

| $016 | out | SPL,r16 | ||

| $017 | sei | ; Enable interrupts | ||

| $018 | <instr> xxx | |||

| … | … | … | ||

Crack Locked ATMEGA128L AVR Chip

Crack Locked ATMEGA128L AVR Chip

Crack Locked ATMEGA128L AVR Chip and readout atmega128l microcontroller flash memory firmware, the secured heximal file of atmega128l mcu can be deciphered from its flash memory;

Crack Locked ATMEGA128L AVR Chip and readout atmega128l microcontroller flash memory firmware, the secured heximal file of atmega128l mcu can be deciphered from its flash memory;

When the WDE is written to logic one, the Watchdog Timer is enabled, and if the WDE is written to logic zero, the Watchdog Timer function is disabled to break off atmega128l chipset fuse bit. WDE can only be cleared if the WDCE bit has logic level one. To disable an enabled Watchdog Timer, the following procedure must be followed:

- In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE even though it is set to one before the disable operation starts

- Within the next four clock cycles, write a logic 0 to This disables the Watchdog

- Bits .0 – WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1, and 0

The WDP2, WDP1, and WDP0 bits determine the Watchdog Timer prescaling when the Watch- dog Timer is enabled. The different prescaling values and their corresponding Timeout Periods are shown in Table 17.

rompa el chip ATMEGA128L avr bloqueado y lea el firmware de la memoria flash del microcontrolador atmega128l, el archivo heximal seguro de atmega128l mcu se puede descifrar desde su memoria flash

The following code example shows one assembly and one C function for turning off the WDT. The example assumes that interrupts are controlled (for example, by disabling interrupts glob- ally) so that no interrupts will occur during execution of these functions.

In this mode, the Watchdog Timer is initially disabled, but can be enabled by writing the WDE bit to 1 without any restriction. A timed sequence is needed when changing the Watchdog Time-out period or disabling an enabled Watchdog Timer by breaking atmega128l microcontroller flash memory. To disable an enabled Watchdog Timer and/or changing the Watchdog Time-out, the following procedure must be followed:

- In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit

- Within the next four clock cycles, in the same operation, write the WDE and WDP bits as desired, but with the WDCE bit cleared

Copy AVR Microcontroller ATMEGA128 Flash Heximal

Copy AVR Microcontroller ATMEGA128 Flash Heximal

Copy AVR Microcontroller ATMEGA128 Flash Heximal needs to unlock avr secured mcu atmega128 protection, the un-encrypted avr microprocessor atmega128 flash memory binary will be extracted;

Copy AVR Microcontroller ATMEGA128 Flash Heximal needs to unlock avr secured mcu atmega128 protection, the un-encrypted avr microprocessor atmega128 flash memory binary will be extracted

The Power-on Reset will not work unless the supply voltage has been below VPOT (falling), VBOT may be below nominal minimum operating voltage for some devices. For devices where this is the case, the device is tested down to VCC = VBOT during the production test to break avr atmega128 mcu fuse bit and readout program. This guarantees that a Brown-out Reset will occur before VCC drops to a voltage where correct operation of the microcontroller is no longer guaranteed. The test is performed using BOD-LEVEL = 1 for ATmega8L and BODLEVEL = 0 for ATmega8. BODLEVEL = 1 is not applicable for ATmega128;

copia AVR microcontrolador ATMEGA128 flash heximal necesita para desbloquear avr asegurado mcu atmega128 protección, el no cifrado avr microprocesador atmega128 memoria flash binario será extraído;

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 15 on page 38. The POR is activated whenever VCC is below the detection level. The POR circuit can be used to trigger the Start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter when break atmega128 microcontroller firmware, which determines how long the device is kept in RESET after VCC rise. The RESET signal is activated again, without any delay, when VCC decreases below the detection level.