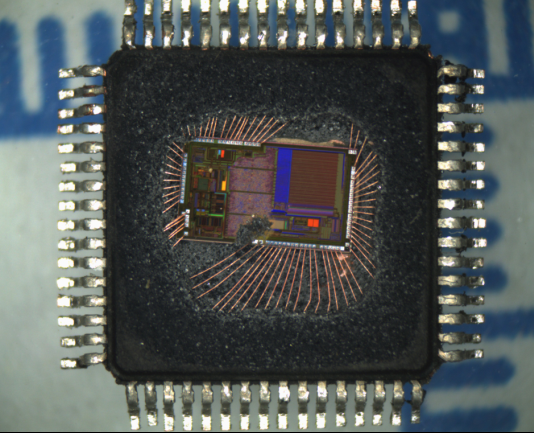

Texas Instruments TMS320F28034PNQ MCU Breaking

Texas Instruments TMS320F28034PNQ MCU Breaking

Texas Instruments TMS320F28034PNQ MCU Breaking is a process to unlock tms320f28034pnq controller’s flash memory and then readout embedded data from microcontroller tms320f28034pnq;

Section 6.2.1 describes the signals. With the exception of the JTAG pins, the GPIO function is the default at reset, unless otherwise mentioned. The peripheral signals that are listed under them are alternate functions. Some peripheral functions may not be available in all devices.

See Table 5-1 for details. Inputs are not 5-V tolerant. All GPIO pins are I/O/Z and have an internal pullup when reverse engineering dsp mcu tms320f28034 flash memory, which can be selectively enabled/disabled on a per-pin basis. This feature only applies to the GPIO pins.

Texas Instruments TMS320F28034PNQ MCU romper es un proceso para desbloquear tms320f28034pnq memoria flash del controlador y luego leer los datos incrustados de tms320f28034pnq microcontrolador;

The pullups on the PWM pins are not enabled at reset. The pullups on other GPIO pins are enabled upon reset. The AIO pins do not have an internal pullup.

When the on-chip VREG is used, the GPIO19, GPIO34, GPIO35, GPIO36, GPIO37, and GPIO38 pins could glitch during power up in order to recover secured dsp tms320f28035 microcontroller flash controller. This potential glitch will finish before the boot mode pins are read and will not affect boot behavior.