Posts Tagged ‘ataque archivo binario de memoria de microordenador protegido’

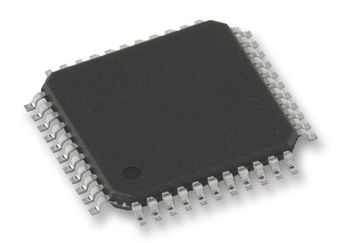

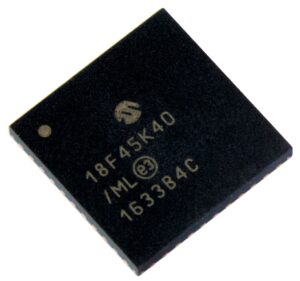

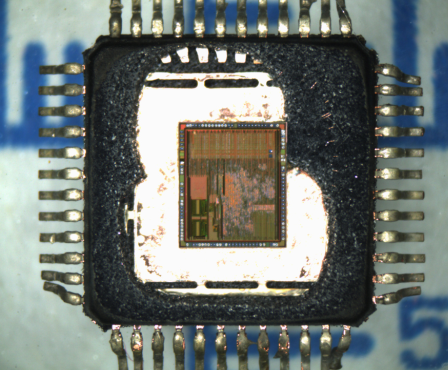

Attack Microchip PIC18F45K40T Controller Memory

Attack Microchip PIC18F45K40T Controller Memory

Attack Microchip PIC18F45K40T Controller Memory is a process to unlock microcontroller pic18f45k40t security fuse bit, and then readout flash memory software from microprocessor pic18f45k40t chipset;

On boards with power traces running longer than six inches in length, it is suggested to use a tank capac- itor for integrated circuits, including microcontrollers, to supply a local power source.

The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 mF to 47 mF.

ataque Microchip PIC18F45K40T controlador de memoria es un proceso para desbloquear microcontrolador pic18f45k40t bit fusible de seguridad, y luego leer el software de memoria flash del microprocesador pic18f45k40t chipset

The first five events will cause a device Reset. The last one event is considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to “Determining the Cause of a Reset” when recover microchip pic18f24k22 locked flash memory code.

When the SLEEP instruction is being executed, the next instruction (PC + 2) is prefetched. For the device to wake-up through an interrupt event, the corresponding Interrupt Enable bit must be enabled, as well as the Peripheral Interrupt Enable bit (PEIE = 1), for every interrupt not in PIR0.

Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled by restoring microcontroller pic18f25k22 memory heximal file, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine.

In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.