Microchip PIC18F4321 Processor Flash Breaking

Microchip PIC18F4321 Processor Flash Breaking

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) by Microchip PIC18F4321 Processor Flash Breaking until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead when Unlock Microcontroller Flash.

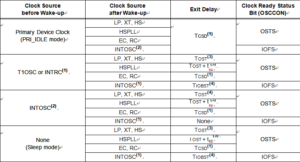

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock by Open IC PIC16F73 Memory,. Exit delays are summarized in below Table.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 23.3 “Two-Speed Start-up”) or Fail-Safe Clock Monitor (see Section 23.4 “Fail-Safe Clock Monitor”) is enabled, the device may begin execution as soon as the Reset source has cleared when Break Secured MCU PIC16F72 Data.

Execution is clocked by the INTOSC multiplexer driven by the inter- nal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down by Recover IC PIC16LF506 Data.

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

• PRI_IDLE mode, where the primary clock source is not stopped and

• the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source is either already running (PRI_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution when Decrypt Locked IC PIC16LF505 Program. Instruction execution resumes on the first clock cycle following this delay.