Decrypt Microprocessor ATmega1281 Eeprom

Decrypt Microprocessor ATmega1281 Eeprom

Decrypt Microprocessor ATmega1281 Eeprom and extract MCU ATmega1281 code from flash memory, prepare Microcontroller ATmega1281 unit clone by copy the firmware to new MCU unit;

Decrypt Microprocessor ATmega1281 Eeprom and extract MCU ATmega1281 code from flash memory, prepare Microcontroller ATmega1281 unit clone by copy the firmware to new MCU unit

The Instruction Set for Serial Programming follows a 3-byte protocol and is shown in the following table: Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied if breaking PIC16F716 heximal memory.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Under operating conditions, load capacitance for Port 0, ALE/PROG, and PSEN = 100 pF; load capacitance for all other outputs = 80 pF.

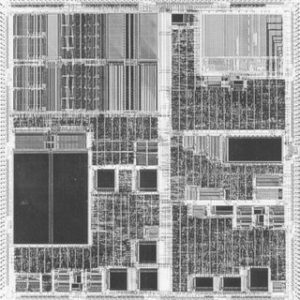

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized. The ATmega1281 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture.

By executing powerful instructions in a single clock cycle, the ATmega1281 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.