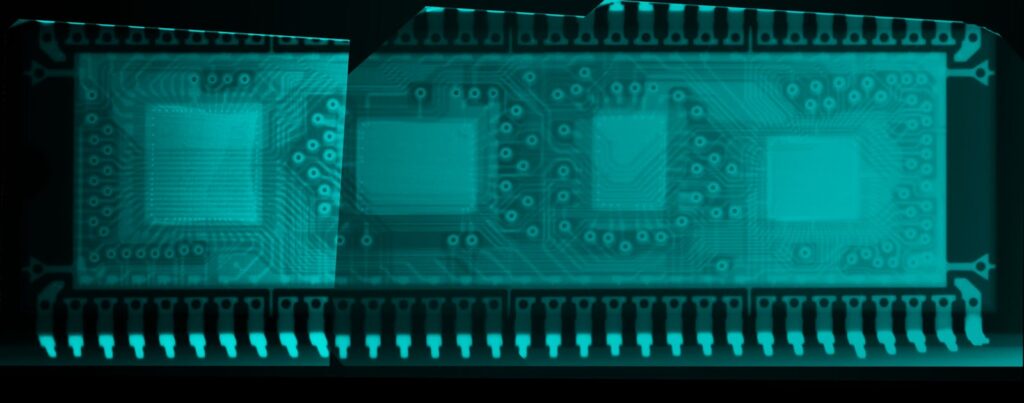

Crack Renesas Microcontroller R5F563NFDDFP#V0 Flash Memory

Crack Renesas Microcontroller R5F563NFDDFP#V0 Flash Memory

Crack Renesas Microcontroller R5F563NFDDFP#V0 Flash Memory and break MCU tamper resistance system, readout locked firmware from secured microprocessor and copy the binary to new MCU;

The number of bus cycles of internal peripheral buses 1 to 6 differs according to the register to be accessed.

When peripheral functions connected to internal peripheral buses 2 to 6 or registers for the external bus control unit (except for bus error related registers) are accessed, the number of divided clock synchronization cycles is added.

The number of divided clock synchronization cycles differs depending on the frequency ratio between ICLK and PCLK (or FCLK) or bus access timing.

зламати мікроконтролер Renesas R5F563NFDDFP#V0 флеш-пам’ять і зламати MCU R5F563NFDDFP#V0 систему стійкості до несанкціонованого доступу, зчитування заблокованої прошивки в форматі двійкового або шістнадцяткового з захищеного мікропроцесора і скопіювати вихідний код прошивки в новий MCU R5F563NFDDFP#V0;

In the peripheral function unit, when the frequency ratio of ICLK is equal to or greater than that of PCLK (or FCLK), the sum of the number of bus cycles for internal main bus 1 and the number of the divided clock synchronization cycles will be one cycle of PCLK (or FCLK) at a maximum.

Therefore, one PCLK (or FCLK) has been added to the number of access cycles shown in Table 4.1.

When the frequency ratio of ICLK is lower than that of PCLK (or FCLK), the subsequent bus access is started from the ICLK cycle following the completion of the access to the peripheral functions to crack renesas mcu R5F52108 Flash memory. Therefore, the access cycles are described on an ICLK basis.

Renesas mikrodenetleyici R5F563NFDDFP # V0 flash belleği kırın ve MCU R5F563NFDDFP # V0 kurcalama direnci sistemini kırın, güvenli mikroişlemciden ikili veya onaltılık biçiminde kilitli bellenimi okuyun ve bellenim kaynak kodunu yeni MCU’ya kopyalayın R5F563NFDDFP # V0;

Note 1. This applies to the number of cycles when the access from the CPU does not conflict with the bus access from the different bus master (DTC).