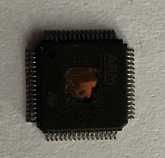

Break STMicroelectronics ARM STM32F070C6 MCU Memory

Break STMicroelectronics ARM STM32F070C6 MCU Memory

Break STMicroelectronics ARM STM32F070C6 MCU Memory will needs to use crack locked bits of microcontroller stm32f070c6 by focus ion beam to disable the protected status, extract embedded firmware from flash memory;

The ARM® Cortex®-M0 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM® Cortex®-M0 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices. The STM32F0xx family has an embedded ARM core and is therefore compatible with all ARM tools and software which become easier when trying to replicate arm mcu stm32f105r8 flash program file.

сломать память микроконтроллера STMicroelectronics ARM STM32F070C6, которая должна будет использовать заблокированные биты микроконтроллера STM32F070C6 путем фокусировки ионного луча, чтобы отключить защищенное состояние, извлечь встроенную прошивку из флэш-памяти;

The device has the following features:

- 6 to 16 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail- critical applications.

- The non-volatile memory is divided into two arrays:

- 32 to 128 Kbytes of embedded Flash memory for programs and data

- Option bytes

- The non-volatile memory is divided into two arrays:

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex®-M0 serial wire) and boot in RAM selection disabled, through our technique we can unlock secured mcu stm32f070rc flash memory

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected