Break PIC18F2610 MCU Flash Memory

Break PIC18F2610 MCU Flash Memory

The power-managed Sleep mode in the PIC18F2610 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction which faciliate the process of Break PIC18F2610 MCU Flash Memory.

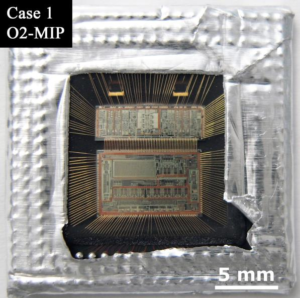

This shuts down the selected oscillator (below Figure) after Break IC PIC12F615 Software. All clock source status bits are cleared. Entering the Sleep mode from any other mode does not require a clock switch to Break IC PIC12F635 Program. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled for the purpose of Break IC PIC16F616 Heximal, it will also continue to run.

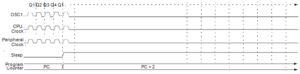

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator block when Break IC PIC12F609 Heximal if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see Section 23.0 “Special Features of the CPU”).

In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up from Crack MCU Software.