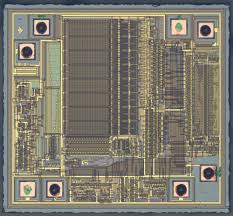

Break Microchip PIC18F2553 Controller Protection

Break Microchip PIC18F2553 Controller Protection

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed by Break Microchip PIC18F2553 Controller Protection. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting. Entry to, and exit from Idle mode, does not affect the state of the IDLEN bit.

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source. The PRI_RUN mode is the normal, full power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled. In this mode, the OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source.

Break Microchip PIC18F2553 Controller Protection

The SEC_RUN mode is the compatible mode to the “clock switching” feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC_RUN mode is entered by setting the SCS1:SCS0 bits to ‘01’. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.