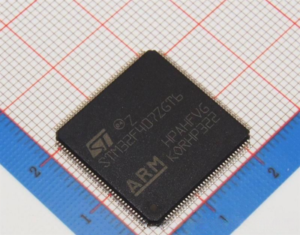

Secured Microcontroller STM32F407ZG Embedded Firmware Restoration

Secured Microcontroller STM32F407ZG Embedded Firmware Restoration

Unlock protective MCU STM32F407ZG Secured Microcontroller security fuse bit and extract program file include binary content of flash memory and eeprom data of rom memory from microprocessor STM32407ZG to fulfill STM32F407ZG Embedded Firmware Restoration;

Unlock protective MCU STM32F407ZG Secured Microcontroller security fuse bit and extract program file include binary content of flash memory and eeprom data of rom memory from microprocessor STM32407ZG to fulfill STM32F407ZG Embedded Firmware Restoration;

The STM32F407ZG is a microcontroller unit (MCU) manufactured by STMicroelectronics. It belongs to the STM32F4 series, which is based on the ARM Cortex-M4 core and it becomes more difficult than other series to recover secured mcu stm32f405rg binary program. This MCU is highly versatile and can be used in various products across different industries. Here are some examples of products where the STM32F407ZG can be utilized:

Embedded Systems: The STM32F407ZG is commonly used in embedded systems for a wide range of applications such as industrial automation, robotics, home automation, and consumer electronics. Its powerful processing capabilities, extensive peripheral set, and low power consumption make it suitable for controlling and managing various functions within these systems.

desbloquee la MCU protectora STM32F407ZG el bit de fusible de seguridad del microcontrolador seguro y extraiga el archivo de programa que incluye el contenido binario de la memoria flash y los datos de EEPROM de la memoria ROM del STM32407ZG del microprocesador para cumplir con STM32F407ZG restauración de firmware integrado;

Communications Equipment: The STM32F407ZG can be employed in communications equipment such as modems, routers, gateways, and network switches. Its high-speed processing capabilities and support for various communication protocols make it ideal for managing data transmission, networking, and connectivity tasks.

Medical Devices: In the medical industry, the STM32F407ZG can be used in devices such as patient monitors, medical imaging systems, infusion pumps, and diagnostic equipment. Its reliability, real-time processing capabilities, and support for safety-critical applications make it well-suited for use in medical devices that require precise control and monitoring.

Automotive Electronics: Automotive applications for the STM32F407ZG include engine control units (ECUs), dashboard displays, infotainment systems, advanced driver assistance systems (ADAS), and vehicle telematics. Its high performance, automotive-grade reliability, and support for automotive communication protocols make it suitable for use in various automotive electronics applications.

отключване на защитен MCU STM32F407ZG защитен микроконтролер сигурност предпазител бит и извличане на програмен файл включва двоично съдържание на флаш памет и eeprom данни на ROM памет от микропроцесорни STM32407ZG за изпълнение STM32F407ZG вграден фърмуер възстановяване;

Consumer Electronics: The STM32F407ZG can be found in consumer electronics products such as smart home devices, wearable gadgets, gaming consoles, multimedia players, and digital cameras. Its processing power, low power consumption, and support for multimedia interfaces make it attractive for implementing advanced features and functionalities in these products.

Industrial Control Systems: Industrial control systems, including programmable logic controllers (PLCs), supervisory control and data acquisition (SCADA) systems, and process automation equipment, often utilize the STM32F407ZG for monitoring and controlling industrial processes. Its robustness, real-time processing capabilities, and support for industrial communication protocols make it suitable for use in industrial environments.

koruyucu MCU’nun kilidini açın STM32F407ZG güvenli mikrodenetleyici güvenlik sigorta biti ve program dosyasını çıkarın, gömülü STM32F407ZG ürün yazılımı geri yüklemesini yerine getirmek için mikroişlemci STM32407ZG’den flash belleğin ikili içeriğini ve rom belleğinin eeprom verilerini dahil edin;

Overall, the STM32F407ZG is a versatile microcontroller that can be employed in a wide range of products across multiple industries, thanks to its powerful features, extensive peripheral set, and flexibility for various applications.

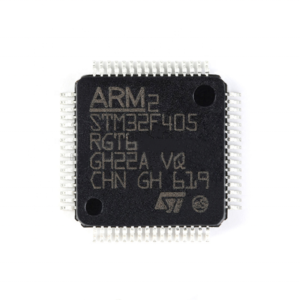

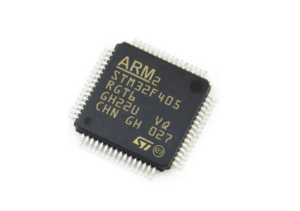

Decode encrypted STM32F405ZG microcontroller flash program

Decode encrypted STM32F405ZG microcontroller flash program

Decode encrypted STM32F405ZG microcontroller flash program starts from attack locked MCU STM32F405ZG tamper resistance system and readout embedded firmware from microprocessor STM32F405ZG flash memory as a binary code or heximal data;

Decode encrypted STM32F405ZG microcontroller flash program starts from attack locked MCU STM32F405ZG tamper resistance system and readout embedded firmware from microprocessor STM32F405ZG flash memory as a binary code or heximal data;

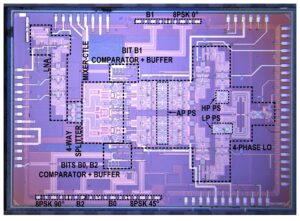

Manufacturing an STM32F405 microcontroller involves several steps and processes. Here’s a general overview:

Design Phase: This involves designing the STM32F405 microcontroller, which includes the architecture, circuitry, and functionalities. STMicroelectronics, the manufacturer of STM32 microcontrollers, typically handles this phase.

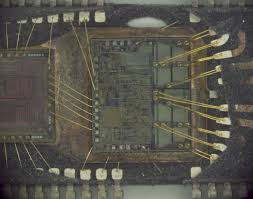

Silicon Wafer Production: The microcontroller’s design is etched onto a silicon wafer using lithography techniques. This process is highly complex and involves creating multiple layers of the integrated circuit.

decodificar STM32F405ZG programa flash de microcontrolador encriptado comienza desde el sistema de resistencia a la manipulación de la MCU STM32F405ZG bloqueado por ataque y lectura del firmware integrado del microprocesador STM32F405ZG la memoria flash como código binario o datos hexaimales;

Wafer Testing: After the silicon wafer is processed, it undergoes testing to ensure that the individual microcontrollers on the wafer meet quality standards. Defective units are marked for later disposal.

Die Separation: The wafer is cut into individual dies, each containing a single STM32F405 microcontroller.

Packaging: Each die is then packaged into a protective housing, which provides electrical connections and protection from environmental factors.

Testing: The packaged microcontrollers undergo rigorous testing to ensure functionality and quality. This includes both electrical and functional tests.

декодиране криптиран STM32F405ZG микроконтролер флаш програма започва от атака заключена MCU STM32F405ZG система за устойчивост на подправяне и четене вграден фърмуер от микропроцесор STM32F405ZG флаш памет като двоичен код или heximal данни;

Programming: The microcontrollers are programmed with the firmware necessary to operate them and copy locked microprocessor stm32f405zg memory heximal file. This firmware typically includes the STM32F405’s initial bootloader and any other necessary software.

Quality Control: Throughout the manufacturing process, quality control measures are implemented to ensure that the finished products meet specifications and standards.

Distribution: Once the microcontrollers pass all quality checks, they are ready for distribution to customers, typically electronic device manufacturers who will integrate them into their products.

It’s important to note that manufacturing microcontrollers like the STM32F405 involves highly specialized equipment and expertise, and is typically carried out by semiconductor fabrication facilities (fabs) with significant investment and infrastructure.

şifreli STM32F405ZG mikrodenetleyici flash programının kodunu çözmek, saldırı kilitli MCU’dan STM32F405ZG kurcalamaya karşı direnç sisteminden başlar ve mikroişlemci STM32F405ZG flash bellekten gömülü bellenimi ikili kod veya onaltılık veri olarak okur;

Unless you have the resources and expertise to set up such a facility, manufacturing STM32F405 microcontrollers would not be feasible on an individual or small scale. Instead, you would typically purchase these microcontrollers from authorized distributors or directly from STMicroelectronics.

Reverse engineering MCU microchip STM32F407IG flash memory

Reverse engineering MCU microchip STM32F407IG flash memory

Reverse engineering MCU microchip STM32F407IG flash memory to attack tamper resistance system of STM32F407IG microcontroller encryption and its fuse bit, extract program file from STM32F407IG microprocessor’s flash memory and dump source code in the format of binary file or heximal data to new STM32F407IG microcomputer;

Reverse engineering MCU microchip STM32F407IG flash memory to attack tamper resistance system of STM32F407IG microcontroller encryption and its fuse bit, extract program file from STM32F407IG microprocessor’s flash memory and dump source code in the format of binary file or heximal data to new STM32F407IG microcomputer;

The STM32F407IG microcontroller can be used in a wide range of products and applications across various industries due to its powerful features and versatility. Here are some examples of products and industries where the STM32F407IG can be employed:

Industrial Automation: The STM32F407IG can be used in industrial control systems, PLCs (Programmable Logic Controllers), motor control applications, and process automation systems. Its rich set of peripherals, including ADCs, DACs, timers, and communication interfaces, make it suitable for controlling and monitoring industrial processes.

Consumer Electronics: The STM32F407IG can be found in various consumer electronics products such as smart home devices, home appliances, audio systems, gaming peripherals, and wearable devices. Its low-power features, USB connectivity, and advanced processing capabilities make it ideal for such applications.

thiết kế ngược vi mạch MCU STM32F407IG bộ nhớ flash để tấn công hệ thống chống giả mạo mã hóa vi điều khiển STM32F407IG và bit cầu chì của nó, trích xuất tệp chương trình từ bộ nhớ flash của bộ vi xử lý STM32F407IG và kết xuất mã nguồn ở định dạng tệp nhị phân hoặc dữ liệu heximal sang máy vi tính STM32F407IG mới;

Medical Devices: In the medical industry, the STM32F407IG can be used in devices such as patient monitoring systems, infusion pumps, medical imaging equipment, and portable diagnostic devices. Its real-time processing capabilities, high-resolution ADCs, and communication interfaces enable the development of advanced medical devices.

Automotive: The STM32F407IG can be employed in automotive applications including engine control units (ECUs), dashboard systems, infotainment systems, and advanced driver assistance systems (ADAS). Its CAN interfaces, high-speed processing, and robust design make it suitable for automotive electronics.

Internet of Things (IoT): The STM32F407IG can be used in IoT devices and edge computing applications where connectivity, processing power, and low-power operation are essential. It can be found in smart sensors, IoT gateways, industrial IoT devices, and smart city infrastructure.

रिवर्स इंजीनियरिंग एमसीयू माइक्रोचिप STM32F407IG STM32F407IG माइक्रोकंट्रोलर एन्क्रिप्शन और उसके फ्यूज बिट के छेड़छाड़ प्रतिरोध प्रणाली पर हमला करने के लिए फ्लैश मेमोरी, STM32F407IG माइक्रोप्रोसेसर की फ्लैश मेमोरी से प्रोग्राम फ़ाइल निकालें और बाइनरी फ़ाइल या हेक्सिमल डेटा के प्रारूप में स्रोत कोड को नए STM32F407IG माइक्रो कंप्यूटर पर डंप करें;

Communications: The STM32F407IG can be used in networking equipment such as routers, switches, and gateways. Its Ethernet MAC controller, USB connectivity, and high-speed processing capabilities make it suitable for handling network protocols and data processing tasks.

Aerospace and Defense: The STM32F407IG can be utilized in aerospace and defense applications including avionics systems, unmanned aerial vehicles (UAVs), navigation systems, and military communication equipment. Its reliability, processing power, and advanced peripherals make it suitable for demanding aerospace and defense environments.

Educational and Hobbyist Projects: The STM32F407IG is also popular among students, hobbyists, and makers for educational projects, DIY electronics, robotics, and prototyping due to its accessibility, affordability, and rich feature set.

Overall, the STM32F407IG microcontroller can be used in a diverse range of products and industries, thanks to its advanced features, flexibility, and performance capabilities. Its popularity and widespread adoption make it a go-to choice for embedded system development across various domains.

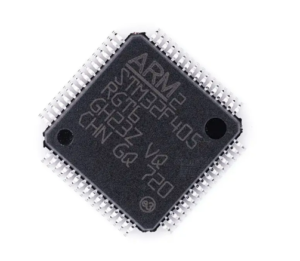

Protective STM32F405VG Microprocessor Content Restoration

Protective STM32F405VG Microprocessor Content Restoration

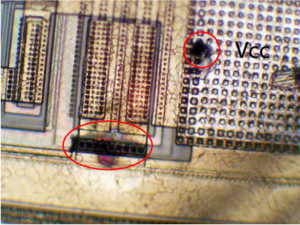

Protective STM32F405VG Microprocessor Content Restoration is a process to unlock the secured microcontroller STM32F405VG readout-protection system and copy embedded firmware from STM32F405VG flash memory in the format of binary or heximal;

Protective STM32F405VG Microprocessor Content Restoration is a process to unlock the secured microcontroller STM32F405VG readout-protection system and copy embedded firmware from STM32F405VG flash memory in the format of binary or heximal;

The internal structure of the STM32F405VG microcontroller from STMicroelectronics is complex and includes several key components that enable its functionality. Here’s an overview of the internal structure:

ARM Cortex-M4 Core: The STM32F405VG is built around the ARM Cortex-M4 core, which serves as the central processing unit (CPU). The Cortex-M4 core is a high-performance 32-bit RISC processor designed for embedded applications. It features a Harvard architecture with separate instruction and data buses, a pipelined architecture, and supports a wide range of instructions and addressing modes.

보호 STM32F405VG 마이크로프로세서 콘텐츠 복원은 보안 마이크로컨트롤러 STM32F405VG 판독 보호 시스템의 잠금을 해제하고 보안 MCU STM32F405VG 플래시 메모리에서 임베디드 펌웨어를 바이너리 또는 16진수 형식으로 복사하는 프로세스입니다.

Memory: The microcontroller typically includes various types of memory:

Flash Memory: This is used for storing the firmware (program code) of the microcontroller. The STM32F405VG typically comes with up to 1 MB of Flash memory.

SRAM (Static Random Access Memory): SRAM is used for storing data and variables during program execution. The STM32F405VG typically includes 192 KB of SRAM.

Registers: Registers are small, high-speed memory locations within the CPU used for temporary data storage and for holding control and status information.

Peripherals: The STM32F405VG incorporates a wide range of peripherals, including but not limited to:

USART, SPI, I2C interfaces for serial communication.

ADC (Analog-to-Digital Converter) and DAC (Digital-to-Analog Converter) channels for analog signal processing.

CAN (Controller Area Network) interfaces for automotive and industrial applications.

USB (Universal Serial Bus) interface for connectivity with external devices.

Timers, PWM (Pulse Width Modulation) channels, and GPIO (General-Purpose Input/Output) pins for various timing and control functions.

Phục hồi nội dung bảo vệ STM32F405VG vi xử lý là một quá trình để mở khóa vi điều khiển bảo mật STM32F405VG hệ thống bảo vệ đọc và sao chép phần sụn nhúng từ bộ nhớ MCU STM32F405VG flash được bảo mật ở định dạng nhị phân hoặc heximal;

DMA (Direct Memory Access) controller for efficient data transfer between peripherals and memory without CPU intervention.

Clock and Reset Management: The microcontroller includes a clock management unit responsible for generating and distributing clock signals to different parts of the device. It also includes a reset controller that manages the reset signals and initializes the device during power-up.

Power Management: Power management features are integrated into the microcontroller to regulate power consumption and optimize energy efficiency. This includes various low-power modes and features such as voltage scaling to adjust the operating voltage based on performance requirements.

Bus Matrix: The bus matrix is responsible for managing the data flow between the different components of the microcontroller, ensuring efficient communication and access to resources.

सुरक्षात्मक STM32F405VG माइक्रोप्रोसेसर सामग्री बहाली रीडआउट-प्रोटेक्शन सिस्टम STM32F405VG सुरक्षित माइक्रोकंट्रोलर को अनलॉक करने और सुरक्षित एमसीयू STM32F405VG फ्लैश मेमोरी से बाइनरी या हेक्सिमल के प्रारूप में एम्बेडेड फर्मवेयर कॉपी करने की एक प्रक्रिया है;

Debug and Trace Unit: The microcontroller includes a debug and trace unit that facilitates software debugging and system analysis by providing features such as breakpoint control, watchpoints, and real-time tracing of program execution.

Overall, the internal structure of the STM32F405VG is designed to provide a balance of performance, flexibility, and power efficiency, making it suitable for a wide range of embedded applications.

Copy Locked Microprocessor STM32F407VG Memory Heximal

Copy Locked Microprocessor STM32F407VG Memory Heximal

Copy locked Microprocessor STM32F407VG Memory Heximal can starts from unlock readout-protection mechanism of microcontroller STM32F407VG flash memory and extract embedded firmware of source code from STM32F407VG MCU flash and eeprom memory;

copy locked microprocessor STM32F407VG memory heximal can starts from unlock readout-protection mechanism of microcontroller STM32F407VG flash memory and extract embedded firmware of source code from STM32F407VG MCU flash and eeprom memory;

The STM32F405 finds application across diverse domains, thanks to its versatility and robust performance. Some notable applications include:

Industrial Automation: In industrial automation systems, the STM32F405 facilitates precise control of machinery and processes through its real-time processing capabilities and support for communication protocols such as Modbus, CAN, and Ethernet. From motor control to human-machine interface (HMI) applications, the STM32F405 enables efficient and reliable automation solutions.

copiar bloqueado microprocessador STM32F407VG memória heximal pode começar a partir de desbloquear mecanismo de proteção de leitura de microcontrolador STM32F407VG memória flash e extrair firmware incorporado do código-fonte de STM32F407VG memória flash MCU e eeprom;

Consumer Electronics: In consumer electronics devices ranging from smart home appliances to portable gadgets, the STM32F405 powers innovative features such as touchscreens, wireless connectivity, and multimedia playback. Its low-power modes and efficient processing ensure optimal performance and extended battery life, enhancing the user experience.

Internet of Things (IoT): With built-in support for connectivity standards like Ethernet, Wi-Fi, and Bluetooth, the STM32F405 serves as a cornerstone for IoT devices and edge computing applications. Whether it’s collecting sensor data, transmitting telemetry to the cloud, or orchestrating local processing tasks, the STM32F405 offers the performance and connectivity required for IoT deployments.

копіювання заблокованого мікропроцесора STM32F407VG шістнадцяткової пам’яті може запускатися з розблокування механізму захисту від зчитування мікроконтролера STM32F407VG флеш-пам’яті та вилучення вбудованої прошивки вихідного коду з STM32F407VG флеш-пам’яті MCU та EEPROM;

The STM32F405 microcontroller epitomizes the convergence of performance, versatility, and efficiency in embedded systems design. With its powerful ARM Cortex-M4 core, rich peripheral set, and integrated features, it empowers developers to realize their creative visions and tackle diverse challenges across industries.

کپی قفل شده میکروپروسسور STM32F407VG حافظه هگزیمال می تواند از مکانیسم باز کردن قفل حفاظت از میکروکنترلر STM32F407VG حافظه فلش شروع می شود و استخراج سیستم عامل تعبیه شده از کد منبع از STM32F407VG فلش MCU و حافظه eeprom؛

Whether it’s driving industrial automation, powering consumer electronics, or enabling the IoT revolution, the STM32F405 stands as a testament to the enduring impact of innovation in embedded technology. As the demand for smarter, more connected devices continues to grow, the STM32F405 remains a steadfast ally for developers pushing the boundaries of what’s possible in the world of embedded systems.

Recover Secured MCU STM32F405RG Binary Program

Recover Secured MCU STM32F405RG Binary Program

Recover secured MCU STM32F405RG binary program or heximal file from its locked flash memory needs to crack arm encrypted STM32F405RG microcontroller fuse bit and extract encrypted microprocessor STM32F405RG embedded firmware;

Recover secured MCU STM32F405RG binary program or heximal file from its locked flash memory needs to crack arm encrypted STM32F405RG microcontroller fuse bit and extract encrypted microprocessor STM32F405RG embedded firmware

In the realm of embedded systems, where efficiency, versatility, and performance are paramount, the STM32F405 microcontroller stands out as a formidable choice. Developed by STMicroelectronics, the STM32F405 series combines advanced features, ample connectivity options, and robust processing capabilities, making it a preferred solution for a diverse range of applications. In this article, we delve into the capabilities and potential of the STM32F405, exploring its key features, applications, and why it’s a compelling choice for embedded developers.

recuperar MCU seguro STM32F405RG programa binário ou arquivo heximal de sua memória flash bloqueada precisa quebrar braço criptografado STM32F405RG microcontrolador fusível bit e extrair microprocessador criptografado STM32F405RG firmware incorporado;

Key Features: The STM32F405 microcontroller boasts an impressive array of features that empower developers to create sophisticated embedded systems. Here are some of its key attributes:

ARM Cortex-M4 Core: At the heart of the STM32F405 lies the ARM Cortex-M4 processor, renowned for its high-performance computing capabilities and energy efficiency. With a clock speed of up to 168 MHz and a floating-point unit (FPU), the Cortex-M4 enables fast and precise mathematical computations, making it ideal for a wide range of applications including signal processing, motor control, and real-time control systems.

відновити захищену MCU STM32F405RG двійкову програму або шістнадцятковий файл із заблокованої флеш-пам’яті, потрібно зламати зашифровану STM32F405RG мікроконтролера біт запобіжника та витягти зашифровану мікропроцесорну STM32F405RG вбудовану прошивку;

Abundant Peripheral Interfaces: The STM32F405 offers an extensive set of peripheral interfaces which can be applied for Microcontroller flash binary file recovery, including multiple UARTs, SPI, I2C, USB, and Ethernet controllers, providing ample connectivity options for interfacing with various sensors, actuators, displays, and communication devices. This versatility enables developers to design feature-rich embedded systems tailored to their specific requirements.

بازیابی امن MCU STM32F405RG برنامه دودویی و یا فایل هگزیمال از حافظه فلش قفل شده خود را نیاز به کرک بازوی رمزگذاری شده STM32F405RG میکروکنترلر فیوز بیت و استخراج ریز پردازنده رمزگذاری شده STM32F405RG سیستم عامل تعبیه شده؛

Rich Integrated Features: Equipped with onboard Flash memory, SRAM, and EEPROM, the STM32F405 eliminates the need for external memory components, reducing board complexity and cost. Additionally, advanced features such as DMA controllers, timers, analog-to-digital converters (ADCs), and digital-to-analog converters (DACs) enhance system performance and efficiency, enabling seamless integration of complex functionalities.

Copy Infineon Locked MCU MB90F342CAPFR-G Flash Heximal

Copy Infineon Locked MCU MB90F342CAPFR-G Flash Heximal

Copy Infineon Locked MCU MB90F342CAPFR-G Flash Heximal to new microcontroller, unlock fujitsu MB90F342CAP secured microcontroller flash memory and clone MB90F342E flash firmware to new microprocessor;

Copy Infineon Locked MCU MB90F342CAPFR-G Flash Heximal to new microcontroller, unlock fujitsu MB90F342CAP secured microcontroller flash memory and clone MB90F342E flash firmware to new microprocessor;

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device’s electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

Copiez le micrologiciel intégré flash INFINEON verrouillé MCU MB90F342CAPFR-G des données heximales ou du fichier binaire sur le nouveau microcontrôleur, déverrouillez la mémoire flash sécurisée du microprocesseur FUJITSU MB90F342CAP et répliquez le programme MB90F342E sur une nouvelle unité clonée par microprocesseur ;

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

The oscillation time of the oscillator is the time it takes for the amplitude of the oscillations to reach 90%. For crystal oscillators, this time is between several ms and several tens of ms to reverse engineering MB90F345CA microcontroller flash memory, for ceramic oscillators the time is between several hundred ms and several ms, and for an external clock, the time is 0 ms.

Kopieren Sie die von INFINEON gesperrte MCU MB90F342CAPFR-G-Flash-eingebettete Firmware von Heximaldaten oder Binärdateien auf den neuen Mikrocontroller, entsperren Sie den FUJITSU MB90F342CAP-gesicherten Mikroprozessor-Flash-Speicher und replizieren Sie das MB90F342E-Programm auf die neue geklonte Mikroprozessoreinheit;

Resolution : Analog variation that is recognized by the A/D converter.

Non linearity error

Differential linearity error : The deviation between the actual conversion characteristics and a line that joins the

zero-transition line ( “00 0000 0000” ¬ ® “00 0000 0001” ) to the full-scale transition line

( “11 1111 1110” ¬ ® “11 1111 1111” ) . : Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal value.

Use the device with external circuits of the following output impedance for analog inputs :

Recommended output impedance of external circuits are : Approx. 1.5 kL or lower (4.0 V £ AVCC £ 5.5 V,

sampling period = 0.5 ms)

Restoring Infineon MB90F342APFV-G MCU Flash Firmware

Restoring Infineon MB90F342APFV-G MCU Flash Firmware

Restoring Infineon MB90F342APFV-G MCU Flash Firmware needs to unlock Fujitsu MB90F342ES microcontroller secured IC flash memory and then dump flash memory binary to new microcontroller MB90F342APFV;

Restoring Infineon MB90F342APFV-G MCU Flash Firmware needs to unlock Fujitsu MB90F342ES microcontroller secured IC flash memory and then dump flash memory binary to new microcontroller MB90F342APFV;

This parameter is based on VSS = AVSS = 0 V

*2: Set AVCC and VCC to the same voltage. Make sure that AVCC does not exceed VCC and that the voltage at the analog inputs does not exceed AVCC when the power is switched on.

*3: VI and VO should not exceed VCC + 0.3 V. VI should not exceed the specified ratings. However if the maximum current to/from an input is limited by some means with external components, the ICLAMP rating supersedes the VI rating.

*4: Applicable to pins: P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P70 to P77, P80 to P87, P90 to P97, PA0, PA1

*5: · Applicable to pins: P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47,

відновлення вбудованої прошивки флеш-пам’яті INFINEON MB90F342APFV-G із заблокованим MCU потрібно зламати флеш-пам’ять мікроконтролера FUJITSU MB90F342ES, а потім витягти двійковий код або шістнадцяткові дані на новий мікропроцесор MB90F342APFV

P50 to P57 (Evaluation device : P50 to P55) , P60 to P67, P70 to P77, P80 to P87, P90 to P97, PA0 to PA1

- Use within recommended operating

- Use with DC voltage (current)

- The +B signal should always be applied by using a limiting resistance placed between the +B signal and the

- The value of the limiting resistance should be set so that when the +B signal is applied, the input current to the microcontroller pin does not exceed the rated value, either instantaneously or for prolonged

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input

Az INFINEON MB90F342APFV-G zárolt MCU flash beágyazott firmware-ének helyreállításához fel kell törnie a FUJITSU-t MB90F342ES mikrokontrollerrel biztosított IC flash memóriát, majd bináris kódot vagy heximalis adatokat kell kinyernie az új mikroprocesszorba MB90F342APFV

potential may pass through the protective diode and increase the potential at the VCC pin when restoring secured fujitsu MCU MB90F345CAP heximal code, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V) , the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin

Readout Renesas R7F7010124AFP Locked MCU Flash Content

Readout Renesas R7F7010124AFP Locked MCU Flash Content

Readout Renesas R7F7010124AFP Locked MCU Flash Content needs to firstly crack R7F7010124AFP secured microcontroller fuse bit and then copy flash program in the format of binary to new microprocessor R7F7010124afp;

Readout Renesas R7F7010124AFP Locked MCU Flash Content needs to firstly crack R7F7010124AFP secured microcontroller fuse bit and then copy flash program in the format of binary to new microprocessor R7F7010124afp;

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate.

When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container when copying renesas microcontroller M306NKFH flash program, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded.

kiolvasás A RENESAS védő R7F7010124AFP zárolt MCU flash tartalomnak először fel kell törnie R7F7010124AFP biztonságos mikrovezérlő biztosítékbitjét, majd bináris forráskód vagy hexaximális adatok formájában flash programot kell másolnia az új mikroprocesszorra R7F7010124AFP

The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized when reading renesas microprocessor R5F212AASD flash binary file. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

зчитування захисного R7F7010124AFP заблокованого вмісту мікроконтролера потрібно спочатку зламати R7F7010124AFP захищений біт запобіжника мікроконтролера, а потім скопіювати програму флеш-пам’яті у форматі двійкового вихідного коду або шістнадцяткових даних на новий мікропроцесор R7F7010124AFP

Recover RH850 R7F7010303AFP Microcontroller Flash Heximal

Recover RH850 R7F7010303AFP Microcontroller Flash Heximal

Recover RH850 R7F7010303AFP Microcontroller Flash Heximal needs to crack R7F7010303AFP renesas locked MCU protection and then pull the embedded firmware out from microprocessor R7F7010303afp flash memory;

Recover RH850 R7F7010303AFP Microcontroller Flash Heximal needs to crack R7F7010303AFP renesas locked MCU protection and then pull the embedded firmware out from microprocessor R7F7010303afp flash memory;

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed when cracking renesas microcontroller R5F563NFDDF flash memory, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

recuperare il programma flash del microcontroller bloccato RH850 R7F7010303AFP nel formato di file binario o dati esimali deve crackare la protezione MCU RENESAS protetta da R7F7010303AFP e quindi estrarre il firmware incorporato dalla memoria flash crittografata del microprocessore RENESAS R7F7010303afp;

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices.

Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to power supply or GND via a resistor if there is a possibility that it will be an output pin to attack renesas R5F5111FAD mcu flash memory. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

recuperați programul flash de microcontroler blocat RH850 R7F7010303AFP în format de fișier binar sau de date heximale trebuie să spargă protecția MCU RENESAS securizată R7F7010303AFP și apoi scoateți firmware-ul încorporat din memoria flash criptată a microprocesorului RENESAS R7F7010303afp;