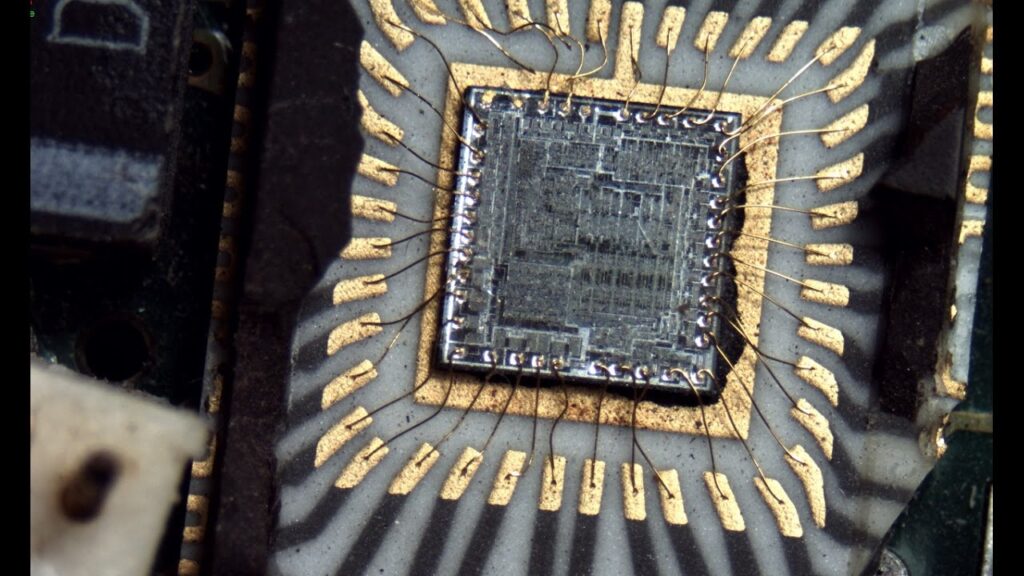

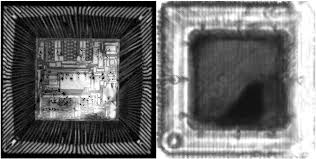

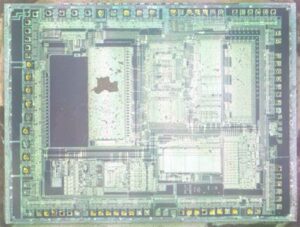

Restoring PIC18F66K80 MCU Controller Embedded Heximal

Restoring PIC18F66K80 MCU Controller Embedded Heximal

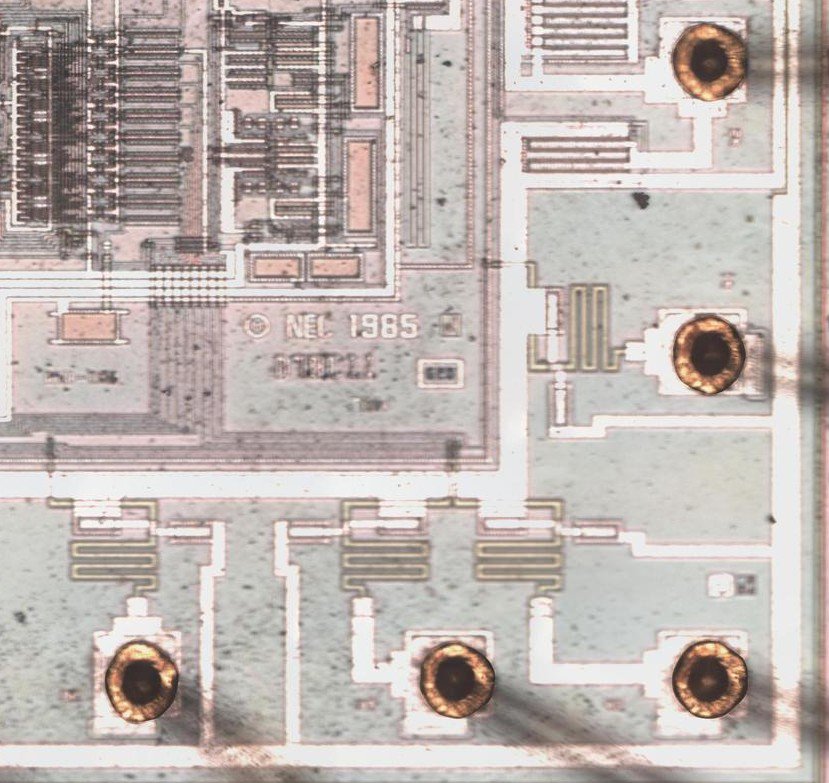

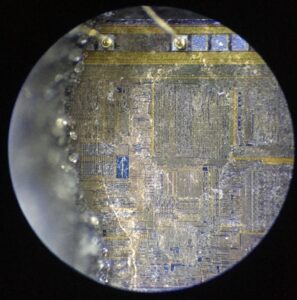

Restoring PIC18F66K80 MCU Controller Embedded Heximal from encrypted flash and eeprom memory, unlock security fuse bit of mcu pic18f66k80 by focus ion beam and extract mcu code;

Using the internal oscillator as the clock source elimi- nates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct oscillator configurations, which are determined by the FOSCx Configuration bits, are available:

restaurar PIC18F66K80 firmware embutido microprocessador bloqueado, incluindo dados heximais da memória flash criptografada e arquivo binário da memória eeprom, desbloquear bit de fusível de segurança do MCU PIC18F66K80 por feixe de íons de foco e extrair microcontrolador protetor PIC18F66K80 código-fonte;

- In INTIO1 mode, the OSC2 pin (RA6) outputs FOSC/4, while OSC1 functions as RA7 for digital input and output.

In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6. Both are available as digital input and output ports.

The 4x Phase Lock Loop (PLL) can be used with the HF-INTOSC to produce faster device clock speeds than are normally possible with the internal oscillator sources to ensure the success . When enabled, the PLL produces a clock speed of 16 MHz or 64 MHz.

بازگرداندن PIC18F66K80 سیستم عامل جاسازی شده ریز پردازنده قفل شده از جمله داده های هگزیمال از حافظه فلش رمزگذاری شده و فایل باینری از حافظه eeprom، باز کردن فیوز امنیتی بیت از PIC18F66K80 MCU توسط پرتو یون تمرکز و استخراج میکروکنترلر محافظ PIC18F66K80 کد منبع؛

PLL operation is controlled through software. The control bits, PLLEN (OSCTUNE<6>) and PLLCFG (CONFIG1H<4>), are used to enable or disable its operation. The PLL is available only to HF-INTOSC. The other oscillator is set with HS and EC modes. Additionally, the PLL will only function when the selected output frequency is either 4 MHz or 16 MHz (OSCCON<6:4> = 111, 110 or 101) when duplicating pic18f26k20 source code.

Like the INTIO modes, there are two distinct INTPLL modes available:

восстановление PIC18F66K80 заблокированной встроенной прошивки микропроцессора, включая шестнадцатеричные данные из зашифрованной флэш-памяти и двоичный файл из памяти EEPROM, разблокировка бита предохранителя MCU PIC18F66K80 фокусировочным ионным пучком и извлечение защитного микроконтроллера PIC18F66K80 исходный код;

- In INTPLL1 mode, the OSC2 pin outputs FOSC/4, while OSC1 functions as RA7 for digital input and output. Externally, this is identical in appearance to INTIO1.

In INTPLL2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output. Externally, this is identical to INTIO2.

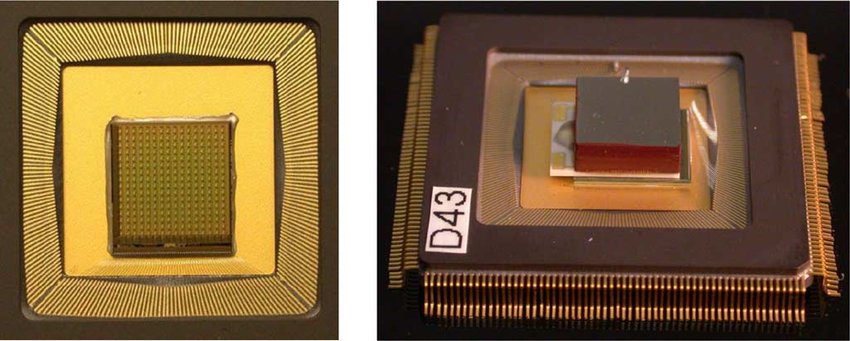

Microchip MCU PIC18F65K80 Heximal Recovery

Microchip MCU PIC18F65K80 Heximal Recovery

Microchip MCU PIC18F65K80 Heximal Recovery is a process to unlock microcontroller pic18f65k80 secured memory and then readout the embedded firmware from mcu;

The PIC18F66K80 family of devices includes an internal oscillator block which generates two different clock signals. Either clock can be used as the microcontroller’s clock source, which may eliminate the need for an external oscillator circuit on the OSC1 and/or OSC2 pins.

The Internal oscillator consists of three blocks, depending on the frequency of operation. They are HF-INTOSC, MF-INTOSC and LF-INTOSC.

Microchip MCU PIC18F65K80 dados binários ou recuperação de programa heximal é um processo para desbloquear microcontrolador seguro PIC18F65K80 memória flash e memória eeprom fusível protetor bit, ler firmware incorporado, como o código-fonte do microprocessador criptografado PIC18F65K80;

In HF-INTOSC mode, the internal oscillator can provide a frequency ranging from 31 KHz to 16 MHz, with the postscaler deciding the selected frequency (IRCF<2:0>).

The INTSRC bit (OSCTUNE<7>) and MFIOSEL bit

(OSCCON2<0>) also decide which INTOSC provides the lower frequency (500 kHz to 31 KHz). For the HF-INTOSC to provide these frequencies, INTSRC = 1 and MFIOSEL = 0.

Микроконтроллер микросхемы PIC18F65K80 двоичных данных или восстановления шестнадцатеричной программы – это процесс разблокировки защищенного микроконтроллера PIC18F65K80 флэш-памяти и защитного бита памяти EEPROM, считывания встроенной прошивки, такой как исходный код зашифрованного микропроцессора PIC18F65K80;

In HF-INTOSC, the postscaler (IRCF<2:0>) provides the frequency range of 31 kHz to 16 MHz. If HF-INTOSC is used with the PLL, the input frequency to the PLL should be 4 MHz to 16 MHz (IRCF<2:0> = 111, 110 or 101) by breaking microchip pic18f25k80 flash memory.

For MF-INTOSC mode to provide a frequency range of 500 kHz to 31 kHz, INTSRC = 1 and MFIOSEL = 1.

The postscaler (IRCF<2:0>), in this mode, provides the

frequency range of 31 kHz to 500 kHz.

The LF-INTOSC can provide only 31 kHz if INTSRC = 0.

میکروچیپ MCU PIC18F65K80 داده های باینری یا بازیابی برنامه هگزیمال یک فرایند برای باز کردن میکروکنترلر امن PIC18F65K80 حافظه فلش و حافظه eeprom محافظ فیوز بیت، بازخوانی سیستم عامل تعبیه شده مانند کد منبع از ریزپردازنده رمزگذاری شده PIC18F65K80 است؛

The LF-INTOSC provides 31 kHz and is enabled if it is selected as the device clock source. The mode is enabled automatically when any of the following are enabled:

- Power-up Timer (PWRT)

- Fail-Safe Clock Monitor (FSCM)

- Watchdog Timer (WDT)

- Two-Speed Start-up

These features are discussed in greater detail in

Section 28.0 “Special Features of the CPU”.

The clock source frequency (HF-INTOSC, MF-INTOSC or LF-INTOSC direct) is selected by configuring the IRCFx bits of the OSCCON register, as well the INTSRC and MFIOSEL bits. The default frequency on device Resets is 8 MHz.

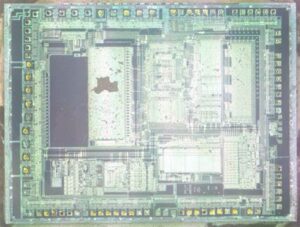

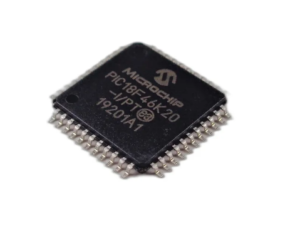

Attack Microchip MCU PIC18F46K80 Protective Flash

Attack Microchip MCU PIC18F46K80 Protective Flash

Attack Microchip MCU PIC18F46K80 Protective Flash and readout MCU embedded firmware, first of all the fuse bit of PIC18F46K80 microcontroller will be unlocked to reset the status of memory;

On boards with power traces running longer than six inches in length, it is suggested to use a tank capac- itor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application.

ataque bloqueado Microchip MCU PIC18F46K80 memória flash protetora e memória eeprom para ler microcontrolador bloqueado PIC18F46K80 firmware incorporado ou código-fonte, em primeiro lugar o bit fusível de microprocessador criptografado PIC18F46K80 será recuperado para redefinir o status da memória e despejar programa binário ou arquivo heximal para fora;

In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 mF to 47 mF. The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging which is also critical when restore pic18f44k20 microchip processor flash memory. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required.

The addition of other components, to help increase the application’s resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1.

атака заблокированного микроконтроллера Microchip PIC18F46K80 защитной флэш-памяти и памяти EEPROM для считывания заблокированного микроконтроллера PIC18F46K80 встроенной прошивки или исходного кода, в первую очередь бит предохранителя зашифрованного микропроцессора PIC18F46K80 будет восстановлен для сброса состояния как памяти, так и дампа двоичной программы или шестнадцатеричного файла;

Other circuit designs may be implemented, depending on the application’s requirements. During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin.

Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements.

حمله قفل شده Microchip MCU PIC18F46K80 حافظه فلش محافظ و حافظه eeprom برای بازخوانی میکروکنترلر قفل شده PIC18F46K80 سیستم عامل جاسازی شده یا کد منبع، اول از همه بیت فیوز میکروپروسسور رمزگذاری شده PIC18F46K80 بهبود خواهد یافت برای تنظیم مجدد وضعیت هر دو حافظه و تخلیه برنامه دودویی یا فایل هگزیمال؛

For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

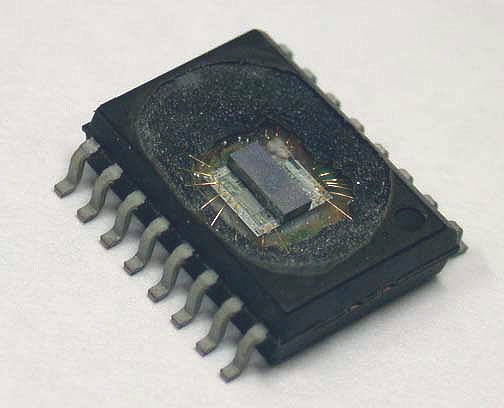

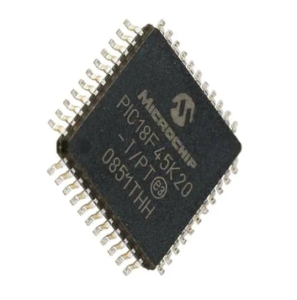

Reverse Protective Microcontroller PIC18F45K80 Flash

Reverse Protective Microcontroller PIC18F45K80 Flash

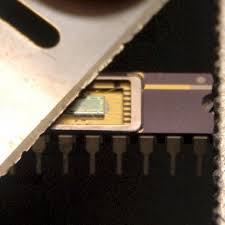

Reverse Protective Microcontroller PIC18F45K80 Flash is a process to unlock mcu pic18f45k80 tamper resistance and break fuse bit, extract MCU code from its flash and eeprom memory;

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1 mF (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

Le microcontrôleur de protection d’ingénierie inverse PIC18F45K80 et la lecture du micrologiciel intégré à partir de la mémoire flash du programme et de la mémoire eeprom des données sont un processus pour déverrouiller la résistance à l’inviolabilité du microprocesseur crypté PIC18F45K80 et casser le bit de fusible, extraire le code source sécurisé du MCU PIC18F45K80 au format de fichier binaire ou de logiciel heximal ;

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capaci- tor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 mF to 0.001 mF. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1 mF in parallel with 0.001 mF).

리버스 엔지니어링 보호 마이크로컨트롤러 PIC18F45K80 및 프로그램 플래시 메모리 및 데이터 eeprom 메모리에서 내장된 펌웨어 판독은 암호화된 마이크로프로세서 PIC18F45K80 변조 저항을 잠금 해제하고 퓨즈 비트를 차단하고 보안 MCU PIC18F45K80 소스 코드를 바이너리 파일 또는 16진수 소프트웨어 형식으로 추출하는 프로세스입니다.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

रिवर्स इंजीनियरिंग सुरक्षात्मक माइक्रोकंट्रोलर PIC18F45K80 और प्रोग्राम फ्लैश मेमोरी और डेटा से एम्बेडेड फर्मवेयर को रीडआउट करें ईप्रोम मेमोरी एन्क्रिप्टेड माइक्रोप्रोसेसर PIC18F45K80 छेड़छाड़ प्रतिरोध को अनलॉक करने और फ्यूज बिट को तोड़ने, सुरक्षित MCU PIC18F45K80 स्रोत कोड को बाइनरी फ़ाइल या हेक्सिमल सॉफ़्टवेयर के प्रारूप में निकालने की एक प्रक्रिया है;

Hack Microchip MCU PIC18F26K80 Secured Flash

Hack Microchip MCU PIC18F26K80 Secured Flash

Hack Microchip MCU PIC18F26K80 Secured Flash and eeprom memory, extract the embedded firmware from microcontroller, the protection over microcontroller pic18f26k80 will be unlocked;

The PIC18F66K80 family provides ample room for application code, from 32 Kbytes to 64 Kbytes of code space. The Flash cells for program memory are rated to last up to 10,000 erase/write cycles.

Le piratage sécurisé de la mémoire flash sécurisée du Microchip MCU PIC18F26K80 et de la mémoire eeprom est un processus permettant de craquer le fusible du microcontrôleur de protection PIC18F26K80 et de lire le micrologiciel intégré du fichier binaire ou des données heximales à partir du microprocesseur crypté PIC18F26K80 ;

Data retention without refresh is conservatively estimated to be greater than 20 years. The Flash program memory is readable and writable. During normal operation, the PIC18F66K80 family also provides plenty of room for dynamic application data with up to 3.6 Kbytes of data RAM.

해킹 보안 마이크로칩 MCU PIC18F26K80 보안 플래시 메모리 및 eeprom 메모리는 보호 마이크로컨트롤러 PIC18F26K80 퓨즈 비트를 크랙하고 암호화된 마이크로프로세서 PIC18F26K80에서 바이너리 파일 또는 16진수 데이터의 내장 펌웨어를 판독하는 프로세스입니다.

The PIC18F25K80 family implements the optional extension to the PIC18 instruction set, adding eight new instructions and an Indexed Addressing mode which are important for attacking pic18f23k20 memory unit. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as ‘C’.

हैक सुरक्षित माइक्रोचिप MCU PIC18F26K80 सुरक्षित फ्लैश मेमोरी और ईप्रोम मेमोरी सुरक्षात्मक माइक्रोकंट्रोलर PIC18F26K80 फ्यूज बिट को क्रैक करने और एन्क्रिप्टेड माइक्रोप्रोसेसर PIC18F26K80 से बाइनरी फ़ाइल या हेक्सिमल डेटा के एम्बेडेड फर्मवेयर को रीडआउट करने की एक प्रक्रिया है;

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

Microchip controller PIC18F25K80 Locked Memory Breaking

Microchip controller PIC18F25K80 Locked Memory Breaking

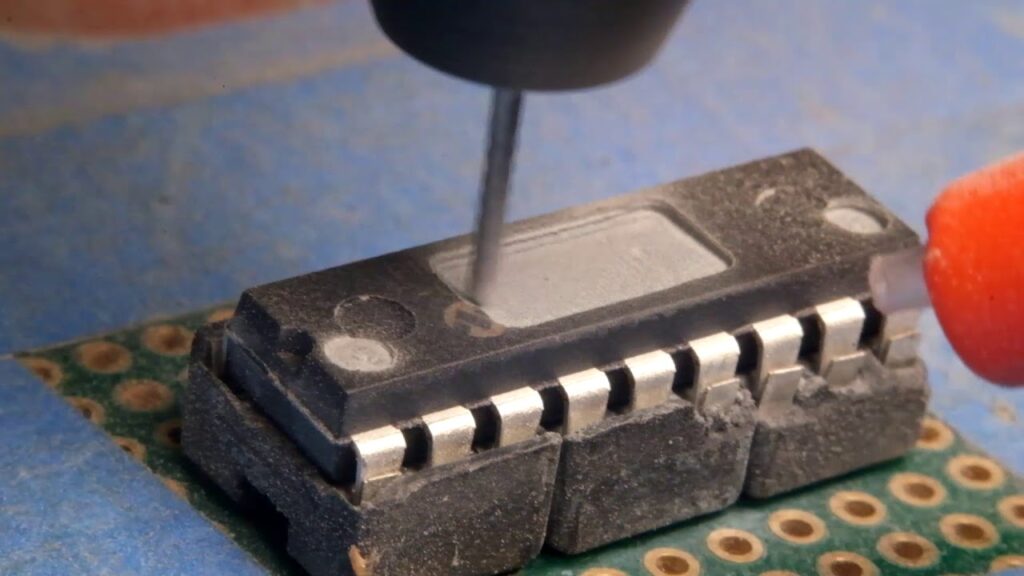

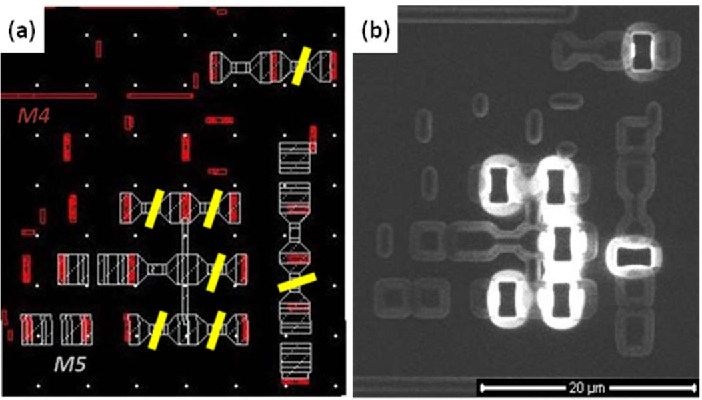

Microchip controller PIC18F25K80 Locked Memory Breaking starts from unlock mcu pic18f25k80 fuse bit by focus ion beam and readout microprocessor flash heximal;

All of the devices in the PIC18F25K80 family incorpo- rate a range of features that can significantly reduce power consumption during operation. Key items include:

La mémoire du programme flash du microcontrôleur sécurisé par puce PIC18F25K80 et la décapsulation de la mémoire de données eeprom commencent à partir du décryptage du MCU de protection PIC18F25K80 fusible par faisceau d’ions focalisé et extrait le microprocesseur crypté PIC18F25K80 du micrologiciel intégré du fichier binaire ou des données heximales ;

- Alternate Run Modes: By clocking the controller from the Timer1 source or the Internal RC oscilla- tor, power consumption during code execution can be reduced.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application’s software design.

마이크로칩 보안 마이크로컨트롤러 PIC18F25K80 플래시 프로그램 메모리 및 eeprom 데이터 메모리 캡슐화는 포커스 이온 빔에 의한 보호 MCU PIC18F25K80 퓨즈 비트를 해독하고 바이너리 파일 또는 16진수 데이터의 암호화된 마이크로프로세서 PIC18F25K80 내장 펌웨어를 추출하는 것부터 시작됩니다.

XLP: An extra low-power BOR and low-power Watchdog timer

All of the devices in the PIC18F25K80 family offer different oscillator options, allowing users a range of choices in developing application hardware as well as unlocking pic18f26k80 flash memory. These include:

- External Resistor/Capacitor (RC); RA6 available

- External Resistor/Capacitor with Clock Out (RCIO)

- Three External Clock modes:

- External Clock (EC); RA6 available

- External Clock with Clock Out (ECIO)

External Crystal (XT, HS, LP)

- A Phase Lock Loop (PLL) frequency multiplier, available to the external oscillator modes which allows clock speeds of up to 64 MHz. PLL can also be used with the internal oscillator.

- An internal oscillator block that provides a 16 MHz clock (±2% accuracy) and an INTOSC source (approximately 31 kHz, stable over temperature and VDD)

- Operates as HF-INTOSC or MF-INTOSC when block is selected for 16 MHz or 500 kHz

- Frees the two oscillator pins for use as additional general purpose I/O

माइक्रोचिप सुरक्षित माइक्रोकंट्रोलर PIC18F25K80 फ्लैश प्रोग्राम मेमोरी और ईप्रोम डेटा मेमोरी डिकैप्सुलेशन फोकस आयन बीम द्वारा डिक्रिप्ट सुरक्षात्मक MCU PIC18F25K80 फ्यूज बिट से शुरू होता है और एन्क्रिप्टेड माइक्रोप्रोसेसर PIC18F25K80 बाइनरी फ़ाइल या हेक्सिमल डेटा के एम्बेडेड फर्मवेयर को निकालता है;

The internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

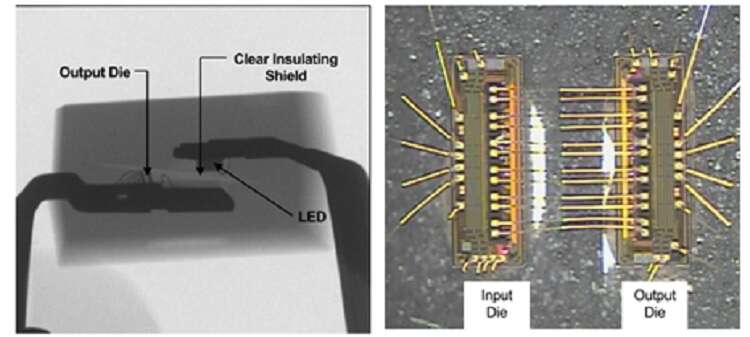

Microprocessor PIC18F46K20 Flash Program Replication

Microprocessor PIC18F46K20 Flash Program Replication

Microprocessor PIC18F46K20 Flash Program Replication needs to crack mcu pic18f46k20 fuse bit by focus ion beam and extract code from embedded IC chip memory;

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL).

These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits will be required also in the process of pic18f24k20 program and data recovery.

La replica del programma flash del microprocessore protetto PIC18F46K20 necessita di crackare il fusibile protetto dell’MCU PIC18F46K20 tramite raggio ionico focalizzato ed estrarre il codice sorgente dal controller del microchip incorporato Dati binari della memoria flash PIC18F46K20 e file esagonale della memoria eeprom;

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 6-2. These operations on the TBLPTR affect only the low-order 21 bits.

wyodrębnij kod źródłowy zabezpieczonego mikrokontrolera PIC18F26J13 zaczynając od bitu bezpiecznika zabezpieczającego PIC18F26J13 mikroprocesora i zrzuć wbudowane oprogramowanie sprzętowe w formacie pliku binarnego lub danych szesnastkowych z zablokowanej pamięci flash MCU PIC18F26J13 lub pamięci eeprom;

TBLPTR is used in reads, writes and erases of the Flash program memory. When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register. When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write.

يبدأ استخراج الكود المصدري لوحدة التحكم الدقيقة المؤمنة PIC18F26J13 من وحدة حماية المعالج الدقيق PIC18F26J13 وتفريغ البرامج الثابتة المضمنة بتنسيق ملف ثنائي أو بيانات سداسية من ذاكرة فلاش MCU المقفلة PIC18F26J13 أو ذاكرة eeprom؛

The holding registers constitute a write block which varies depending on the device.The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

Attack Microchip PIC18F45K20 MCU Memory Protection

Attack Microchip PIC18F45K20 MCU Memory Protection

Attack Microchip PIC18F45K20 MCU Memory Protection and unlock microcontroller pic18f45k20 flash and eeprom memory, read embedded heximal from mcu with programmer;

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in Section 6.5 “Writing to Flash Program Memory”.

Figure 6-2 shows the operation of a table write with program memory and data RAM. Table operations work with byte entities. Tables contain- ing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned for pic18f43k20 flash memory breaking.

protezione della memoria MCU del microchip PIC18F45K20 protetta dall’attacco e sblocco protetto della memoria flash ed eeprom del microcontrollore PIC18F45K20, lettura dei dati esagonali incorporati o del codice sorgente binario dalla memoria flash crittografata PIC18F45K20 del microprocessore e dal firmware incorporato della memoria eeprom con programmatore;

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all ‘0’s.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory.

zabezpieczony przed atakiem mikrochip PIC18F45K20 ochrona pamięci MCU i odblokowanie chronionego mikrokontrolera PIC18F45K20 pamięć flash i eeprom, odczyt osadzonych danych szesnastkowych lub binarnego kodu źródłowego z zaszyfrowanej mikroprocesorem pamięci flash PIC18F45K20 i wbudowanego oprogramowania sprzętowego pamięci eeprom z programatorem;

When EEPGD is set, any subsequent operations will operate on the program memory. The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory.

When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see Section 23.0“Special Features of the CPU”). When CFGS is clear, memory selection access is determined by EEPGD.

Microchip PIC18F44K20 Processor Flash Memory Program Restoration

Microchip PIC18F44K20 Processor Flash Memory Program Restoration

Microchip PIC18F44K20 Processor Flash Memory Program Restoration is a reverse engineering process through which the fuse bit of MCU pic18f44k20 will be located and cracked, then extract locked code from microcontroller memory;

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Il ripristino del programma di memoria flash del microprocessore crittografato PIC18F44K20 di Microchip è un processo di reverse engineering attraverso il quale il bit del fusibile dell’MCU PIC18F44K20 bloccato verrà individuato e violato, quindi verrà estratto il codice sorgente bloccato nel formato di dati binari o file esimale dalla flash incorporata e dall’eeprom del microcontroller PIC18F44K20 protetto. memoria firmware;

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is ‘1’), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute to faciliate the process of attacking mcu pic18f13k50 flash memory. A comparison of the different possible addressing modes when the extended instruction set is enabled.

Przywracanie programu zaszyfrowanej pamięci flash mikroprocesora PIC18F44K20 to proces inżynierii odwrotnej, podczas którego bit bezpiecznika zablokowanego MCU PIC18F44K20 zostanie zlokalizowany i złamany, a następnie wyodrębniony zostanie zablokowany kod źródłowy w formacie danych binarnych lub pliku szesnastkowego z chronionej wbudowanej pamięci flash i eeprom mikrokontrolera PIC18F44K20 pamięć oprogramowania;

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in Section 24.2.1“Extended Instruction Syntax”.

Break PIC18F43K20 Microcontroller Flash Memory

Break PIC18F43K20 Microcontroller Flash Memory

Break PIC18F43K20 Microcontroller Flash Memory is a process to crack mcu pic18f43k20 fuse bit by focus ion beam and then readout MCU heximal;

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifi- cally, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the intro- duction of a new addressing mode for the data memory space.

quebrar a memória flash do microcontrolador de proteção PIC18F43K20 é um processo para desabilitar / atacar o bit de fusível MCU PIC18F43K20 protegido por feixe de íons de foco e, em seguida, ler o firmware incorporado do microprocessador criptografado por microchip, memória flash PIC18F43K20 e memória eeprom no formato de código-fonte heximal ou dados de arquivo binário;

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

взлом флэш-памяти защитного микроконтроллера PIC18F43K20 – это процесс отключения / атаки защищенного плавкого бита MCU PIC18F43K20 с помощью фокуса ионного луча, а затем считывания встроенной прошивки из зашифрованной микрочипом флэш-памяти микропроцессора PIC18F43K20 и памяти EEPROM в формате шестнадцатеричного исходного кода или данных двоичного файла;

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction by . This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode by breaking mcu pic18f14k22 flash memory;

شکستن حافظه فلش میکروکنترلر محافظ PIC18F43K20 فرآیندی است برای غیرفعال کردن/حمله کردن فیوز ایمن MCU PIC18F43K20 توسط پرتو یونی فوکوس و سپس بازخوانی سیستم عامل تعبیه شده از ریزپردازنده رمزگذاری شده با ریزتراشه PIC18F43K20 حافظه فلش منبع و حافظه فایل کد باینری eeprom با فرمت یا فرمت Head.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced (‘a’ = 0) and

The file address argument is less than or equal to 5Fh.