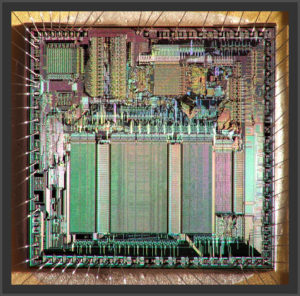

Reverse IC ATmega861V Code

Reverse IC ATmega861V Code

Reverse IC ATmega861V code programming process, disable the protective measurement by unlock microcontroller ATmega861V, extract content from MCU program memory and reprogramme the firmware to new ATmega861V;

Reverse IC ATmega861V code programming process, disable the protective measurement by unlock microcontroller ATmega861V, extract content from MCU program memory and reprogramme the firmware to new ATmega861V

The Compare Output mode (COM2x1:0) bits have two functions. The Waveform Generator uses the COM2x1:0 bits for defining the Output Compare (OC2x) state at the next compare match.

Also, the COM2x1:0 bits control the OC2x pin output source. Figure 70 shows a simplified schematic of the logic affected by the COM2x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM2x1:0 bits are shown if breaking Microcontroller PIC16C65B eeprom.

When referring to the OC2x state, the reference is for the internal OC2x Register, not the OC2x pin. The general I/O port function is overridden by the Output Compare (OC2x) from the Waveform Generator if either of the COM2x1:0 bits are set.

However, the OC2x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC2x pin (DDR_OC2x) must be set as output before the OC2x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC2x state before the output is enabled. Note that some COM2x1:0 bit settings are reserved for certain modes of operation. See “8-bit Timer/Counter Register Description” on page 184 if Recover MCU PIC16F687 software code.

The Waveform Generator uses the COM2x1:0 bits differently in normal, CTC, and PWM modes. For all modes, setting the COM2x1:0 = 0 tells the Waveform Generator that no action on the OC2x Register is to be performed on the next compare match.

For compare output actions in the non-PWM modes refer to Table 88 on page 185. For fast PWM mode, refer to Table 89 on page 185, and for phase correct PWM refer to Table 90 on page 186. A change of the COM2x1:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC2x strobe bits.

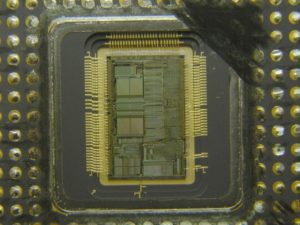

Recover MCU PIC16F648A Firmware

Recover MCU PIC16F648A Firmware

Recover MCU PIC16F648A Firmware from microcontroller PIC16F648A flash memory is the result of MCU cracking, after application of this technique over the master MCU PIC16F648A with original program into it;

Recover MCU PIC16F648A Firmware from microcontroller PIC16F648A flash memory is the result of MCU cracking, after application of this technique over the master MCU PIC16F648A with original program into it

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F648A Product Identification System, at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

FLASH Devices

FLASH devices can be erased and re-programmed electrically. This allows the same device to be used for prototype development, pilot programs and production. A further advantage of the electrically erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip’s PICSTART® Plus, or PRO MATE® II programmers.

Quick-Turnaround-Production

(QTP) Devices Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

Serialized Quick-Turnaround Production (SQTPSM) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential. Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number

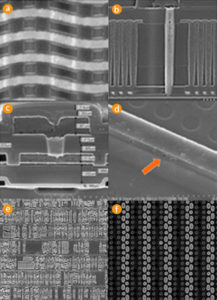

Recover PIC MCU Microchip 16LF506 Firmware

Recover PIC MCU Microchip 16LF506 Firmware

Recover PIC MCU Microchip 16LF506 Firmware and copy program to new Microcontroller PIC16LF506, clone master PIC16LF506 mcu which can provide the same functions as original master Microprocessor;

Recover PIC MCU Microchip 16LF506 Firmware and copy program to new Microcontroller PIC16LF506, clone master PIC16LF506 mcu which can provide the same functions as original master Microprocessor

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options when Recover IC STM32F107RCT6 code.

The General Purpose Registers are used for data and control information under command of the instructions. For the PIC12F510, the register file is composed of 10 Special Function Registers, 6 General Purpose.

Registers and 32 General Purpose Registers accessed For the PIC16F506, the register file is composed of 13 Special Function Registers, 3 General Purpose Registers and 64 General Purpose Registers accessed.

unlock microcontroller PIC16F506 tamper resistance system and extract embedded program data from flash memory

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (see Table 4-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the “core” functions are described in this section for the purpose of chip AT89S8252 flash content copying.

Those related to the operation of the peripheral features are described in the section for each peripheral feature.

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register

as 000u u1uu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits.