Archive for May, 2014

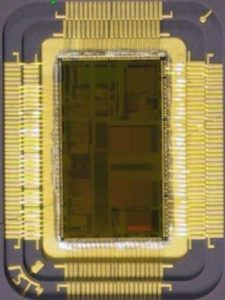

Recover Microcontroller TMS320F2812PGFA Firmware

Recover Microcontroller TMS320F2812PGFA Firmware

We can Recover Microcontroller TMS320F2812PGFA Firmware, please view below the Microcontroller TMS320F2812PGFA features for your reference:

High-Performance Static CMOS Technology

– 150 MHz (6.67-ns Cycle Time)

– Low-Power (1.8-V Core at 135 MHz, 1.9-V Core at 150 MHz, 3.3-V I/O) Design

· JTAG Boundary Scan Support (1)

· High-Performance 32-Bit CPU ( TMS320C28x™)

– 16 x 16 and 32 x 32 MAC Operations

– 16 x 16 Dual MAC

– Harvard Bus Architecture

– Atomic Operations

– Fast Interrupt Response and Processing

– Unified Memory Programming Model

– 4M Linear Program/Data Address Reach

– Code-Efficient (in C/C++ and Assembly)

– TMS320F24x/LF240x Processor Source Code Compatible to Copy microcontroller

· On-Chip Memory

– Flash Devices: Up to 128K x 16 Flash (Four 8K x 16 and Six 16K x 16 Sectors)

– ROM Devices: Up to 128K x 16 ROM

– 1K x 16 OTP ROM

– L0 and L1: 2 Blocks of 4K x 16 Each Single-Access RAM (SARAM)

– H0: 1 Block of 8K x 16 SARAM

– M0 and M1: 2 Blocks of 1K x 16 Each SARAM

· Boot ROM (4K x 16)

– With Software Boot Modes

– Standard Math Tables

· External Interface (2812)

– Over 1M x 16 Total Memory

– Programmable Wait States

– Programmable Read/Write Strobe Timing

– Three Individual Chip Selects

· Endianness: Little Endian

· Clock and System Control

– Dynamic PLL Ratio Changes Supported

– On-Chip Oscillator

– Watchdog Timer Module

· Three External Interrupts

· Peripheral Interrupt Expansion (PIE) Block That Supports 45 Peripheral Interrupts

· Three 32-Bit CPU-Timers

· 128-Bit Security Key/Lock

– Protects Flash/ROM/OTP and L0/L1 SARAM

– Prevents Firmware Reverse-Engineering

· Motor Control Peripherals

– Two Event Managers (EVA, EVB)

– Compatible to 240xA Devices

· Serial Port Peripherals

– Serial Peripheral Interface (SPI)

– Two Serial Communications Interfaces (SCIs), Standard UART

– Enhanced Controller Area Network (eCAN)

– Multichannel Buffered Serial Port (McBSP)

· 12-Bit ADC, 16 Channels

– 2 x 8 Channel Input Multiplexer

– Two Sample-and-Hold

– Single/Simultaneous Conversions

– Fast Conversion Rate: 80 ns/12.5 MSPS

· Up to 56 General-Purpose I/O (GPIO) Pins

· Advanced Emulation Features

– Analysis and Breakpoint Functions

– Real-Time Debug via Hardware

· Development Tools Include

– ANSI C/C++ Compiler/Assembler/Linker

– Code Composer Studio™ IDE

– DSP/BIOS™

– JTAG Scan Controllers(1)

· Low-Power Modes and Power Savings

– IDLE, STANDBY, HALT Modes Supported

– Disable Individual Peripheral Clocks

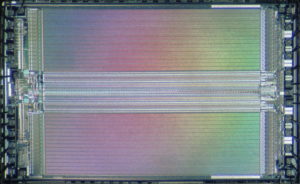

Recover MCU dsPIC30F6013A30IP Firmware

Recover MCU dsPIC30F6013A30IP Firmware

We can Recover MCU dsPIC30F6013A30IP Firmware, please view below MCU DSPIC30F6013A30IP features for your reference:

The dsPIC30F family of DSCs contains a region of on-chip memory used to simplify device programming. This region of memory can store a programming executive, which allows the dsPIC30F to be programmed faster than the traditional means. Once the programming executive is stored to memory by an external programmer (such as Microchip’s MPLAB ICD 2, MPLAB PM3, PRO MATE® II, or MPLAB REAL uses control codes to serially execute instructions on the dsPIC30F device.

This specification describes the ICSP and Enhanced ICSP programming methods. Section 3.0 “Programming Executive Application” describes the programming executive application and Section 5.0 “Device Programming” describes its application programmer’s interface for the host programmer before Recover MCU. Section 11.0 “ICSP™ Mode” describes the ICSP programming method. ICE™), it can then interact with the external programmer to efficiently program devices.

2.1 Hardware Requirements

The programmer and programming executive have a master-slave relationship, where the programmer is the master programming device and the programming executive is the slave.

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for IC Break, MCU attack, MCU Recover, Microcontroller Copy service. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice. Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more information please contact us through email.

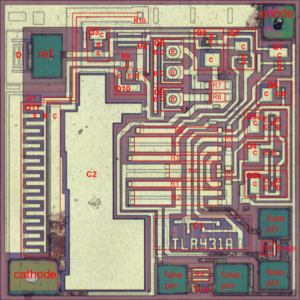

Break IC SST89E58RD2A Software

Break IC SST89E58RD2A Software

We can Break IC SST89E58RD2A Software, below please find the IC SST89E58RD2A features for your reference:

SST89E/V58 / 54 / 52RD2/RD FlashFlex51 MCU

Preliminary FEATURES:

· 8-bit 8051-Compatible Microcontroller (MCU)

· Ten Interrupt Sources at 4 Priority with Embedded SuperFlash Memory to Clone IC

– Four External Interrupt Inputs

– Fully Software Compatible

· Programmable Watchdog Timer

– Development Toolset Compatible

· Programmable Counter Array (PCA)

– Pin-For-Pin Package Compatible

· Four 8-bit I/O Ports (32 I/O Pins)

· SST89E5xRD2 Operation

One 4-bit Port

– 0 to 40 MHz at 5V

· Second DPTR register

· SST89V5xRD2 Operation

· Low EMI Mode (Inhibit ALE)

– 0 to 33 MHz at 3V

· SPI Serial Interface

· 1 KByte Internal RAM

· Standard 12 Clocks per cycle

· Dual Block SuperFlash EEPROM option to double the speed to 6

– 8/16/32 KByte primary block +

· TTL- and CMOS-Compatible Logic 8 KByte secondary block

· Brown-out Detection (128-Byte sector size for both blocks)

· Low Power Modes

– Individual Block Security Lock with SoftLock

– Concurrent Operation during

– Power-down Mode with External In-Application Programming (IAP)

– Idle Mode

– Memory Overlay for Interrupt Support during IAP

· Temperature Ranges:

· Support External Address Range up to 64

– Commercial (0°C to +70°C) KByte of Program and Data Memory

– Industrial (-40°C to +85°C)

· Three High-Current Drive Ports (16 mA each)

· Packages Available

· Three 16-bit Timers/Counters

– 44-lead PLCC

· Full-Duplex, Enhanced UART

– 40-pin PDIP (Port 4 feature

– 44-lead TQFP

– Framing Error Detection

– Automatic Address Recognition

· All non-Pb (lead-free) devices

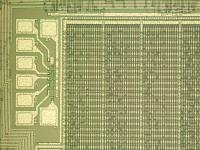

Copy Chip PIC18F252 Flash

Copy Chip PIC18F252 Flash

We can Copy Chip PIC18F252 Flash, please view below Chip PIC18F252 features for your reference:

Power Management Features:

Run: CPU on, Peripherals on

Idle: CPU off, Peripherals on

Sleep: CPU off, Peripherals off

Ultra Low 50nA Input Leakage

Run mode Currents Down to 11 ìA Typical

Idle mode Currents Down to 2.5 ìA Typical

Sleep mode Current Down to 100 nA Typical

Timer1 Oscillator: 900 nA, 32 kHz, 2V

Watchdog Timer: 1.4 ìA, 2V Typical

Two-Speed Oscillator Start-up

· Master Synchronous Serial Port (MSSP) module

Master and Slave modes

· Enhanced Addressable USART module:

– Supports RS-485, RS-232 and LIN/J2602

– RS-232 operation using internal oscillator

block (no external crystal required)

– Auto-wake-up on Start bit

– Auto-Baud Detect

· 10-Bit, up to 13-Channel Analog-to-Digital (A/D)

Flexible Oscillator Structure:

· Four Crystal modes, up to 40 MHz

· 4x Phase Lock Loop (PLL) – Available for Crystal

and Internal Oscillators

· Two External RC modes, up to 4 MHz

· Two External Clock modes, up to 40 MHz

· Internal Oscillator Block:

– Fast wake from Sleep and Idle, 1 ìs typical

– 8 use-selectable frequencies, from 31 kHz to 8 MHz

– Provides a complete range of clock speeds

from 31 kHz to 32 MHz when used with PLL

– User-tunable to compensate for frequency drift

· Secondary Oscillator using Timer1 @ 32 kHz

· Fail-Safe Clock Monitor:

– Allows for safe shutdown if peripheral clock stops

Peripheral Highlights:

Converter module:

– Auto-acquisition capability

– Conversion available during Sleep

· Dual Analog Comparators with Input Multiplexing

· Programmable 16-Level High/Low-Voltage

Detection (HLVD) module:

– Supports interrupt on High/Low-Voltage Detection

Special Microcontroller Features:

· C Compiler Optimized Architecture:

– Optional extended instruction set designed to optimize re-entrant code

· 100,000 Erase/Write Cycle Enhanced Flash

Program Memory Typical

· 1,000,000 Erase/Write Cycle Data EEPROM

Memory Typical

· Flash/Data EEPROM Retention: 100 Years Typical which is important for IC Extraction

· Self-Programmable under Software Control

High-Current Sink/Source 25 mA/25 mA

Three Programmable External Interrupts

Four Input Change Interrupts

Up to 2 Capture/Compare/PWM (CCP) modules,

· Priority Levels for Interrupts

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 4 ms to 131s

one with Auto-Shutdown (28-pin devices)

· Enhanced Capture/Compare/PWM (ECCP)

module (40/44-pin devices only):

– One, two or four PWM outputs

– Selectable polarity

– Programmable dead time

– Auto-shutdown and auto-restart

· Single-Supply 5V In-Circuit Serial

Programming™ (ICSP™) via Two Pins

· In-Circuit Debug (ICD) via Two Pins

· Wide Operating Voltage Range: 2.0V to 5.5V

· Programmable Brown-out Reset (BOR) with

Software Enable Option

Copy Microcontroller PIC12F675 Firmware

Copy Microcontroller PIC12F675 Firmware

We can Copy Microcontroller PIC12F675 Firmware, please view below Microcontroller PIC12F675 features for your reference:

High-Performance RISC CPU:

· Only 35 Instructions to Learn

– All single-cycle instructions except branches

· Operating Speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt Capability

· 8-Level Deep Hardware Stack

· Direct, Indirect, and Relative Addressing modes

Special Microcontroller Features:

· Internal and External Oscillator Options

– Precision Internal 4 MHz oscillator factory calibrated to ±1%

– External Oscillator support for crystals and resonators

– 5 ms wake-up from Sleep, 3.0V, typical

· Power-Saving Sleep mode

· Wide Operating Voltage Range – 2.0V to 5.5V

· Industrial and Extended Temperature Range

· Low-Power Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Brown-out Detect (BOD)

· Watchdog Timer (WDT) with Independent

Oscillator for Reliable Operation

· Multiplexed MCLR/Input Pin

· Interrupt-on-Pin Change

· Individual Programmable Weak Pull-ups

· Programmable Code Protection

· High Endurance Flash/EEPROM Cell

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM Retention: > 40 years

Low-Power Features:

· Standby Current:

– 1 nA @ 2.0V, typical

· Operating Current:

– 8.5 mA @ 32 kHz, 2.0V, typical

– 100 mA @ 1 MHz, 2.0V, typical

· Watchdog Timer Current

– 300 nA @ 2.0V, typical

· Timer1 Oscillator Current:

– 4 mA @ 32 kHz, 2.0V, typical

Peripheral Features:

· 6 I/O Pins with Individual Direction Control

· High Current Sink/Source for Direct LED Drive

· Analog Comparator module with:

– One analog comparator

– Programmable on-chip comparator voltage reference (CVREF) module

– Programmable input multiplexing from device inputs

– Comparator output is externally accessible to Read MCU

· Analog-to-Digital Converter module (PIC12F675):

– 10-bit resolution

– Programmable 4-channel input

– Voltage reference input

· Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Gate Input mode

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins

Recover Chip MC9S08DZ32ACLC Firmware

Recover Chip MC9S08DZ32ACLC Firmware

We can Recover Chip MC9S08DZ32ACLC Firmware, please view below the Chip MC9S08DZ32ACLC features for your reference:

8-Bit HCS08 Central Processor Unit (CPU)

· 40-MHz HCS08 CPU (20-MHz bus)

· HC08 instruction set with added BGND instruction

· Support for up to 32 interrupt/reset sources

On-Chip Memory

· Flash read/program/erase over full operating voltage and temperature

— MC9S08DZ60 = 60K

— MC9S08DZ48 = 48K

— MC9S08DZ32 = 32K

— MC9S08DZ16 = 16K

· Up to 2K EEPROM in-circuit programmable memory;

8-byte single-page or 4-byte dual-page erase sector;

Program and Erase while executing Flash; Erase abort

· Up to 4K random-access memory (RAM)

Power-Saving Modes

· Two very low power stop modes

· Reduced power wait mode

· Very low power real time interrupt for use in run, wait, and stop Clock Source Options

· Oscillator (XOSC) — Loop-control Pierce oscillator;

Crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

· Multi-purpose Clock Generator (MCG) — PLL and FLL modes (FLL capable of 1.5% deviation using internal temperature compensation); Internal reference clock with trim adjustment (trimmed at factory, with trim value stored in flash); External reference with oscillator/resonator options in the process of Copy microcontroller

System Protection

· Watchdog computer operating properly (COP) reset with option to run from backup dedicated 1-kHz internal clock source or bus clock

· Low-voltage detection with reset or interrupt; selectable trip points

· Illegal opcode detection with reset

· Illegal address detection with reset

· Flash block protect

· Loss-of-lock protection

Peripherals

· ADC — 24-channel, 12-bit resolution, 2.5 ìs conversion time, automatic compare function, temperature sensor, internal bandgap reference channel

· ACMPx — Two analog comparators with selectable interrupt on rising, falling, or either edge of comparator output; compare option to fixed internal bandgap reference voltage.

· MSCAN — CAN protocol – Version 2.0 A, B; standard and extended data frames; Support for remote frames; Five receive buffers with FIFO storage scheme; Flexible identifier acceptance filters programmable as: 2 x 32-bit, 4 x 16-bit, or 8 x 8-bit

· SCIx — Two SCIs supporting LIN 2.0 Protocol and SAE J2602 protocols; Full duplex non-return to zero (NRZ); Master extended break generation; Slave extended break detection; Wakeup on active edge.

· SPI — Full-duplex or single-wire bidirectional; Double-buffered transmit and receive; Master or Slave mode; MSB-first or LSB-first shifting

· IIC — Up to 100 kbps with maximum bus loading; Multi-master operation; Programmable slave address; General Call Address; Interrupt driven byte-by-byte data transfer

· TPMx — One 6-channel (TPM1) and one 2-channel (TPM2); Selectable input capture, output compare, or buffered edge-aligned PWM on each channel.

· RTC — (Real-time counter) 8-bit modulus counter with binary or decimal based prescaler; Real-time clock capabilities using external crystal and RTC for precise time base, time-of-day, calendar or task scheduling functions; Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components Input/Output

· 53 general-purpose input/output (I/O) pins and 1 input-only pin

· 24 interrupt pins with selectable polarity on each pin.

· Hysteresis and configurable pull device on all input pins.

· Configurable slew rate and drive strength on all output pins.

Package Options

· 64-pin low-profile quad flat-pack (LQFP) — 10×10 mm

· 48-pin low-profile quad flat-pack (LQFP) — 7×7 mm

· 32-pin low-profile quad flat-pack (LQFP) — 7×7 mm

Copy IC PIC18F458 Binary

Copy IC PIC18F458 Binary

Copy IC PIC18F458 Binary from its locked memory include flash and eeprom, the firmware will be same as original Microcontroller PIC18F458 program and can be replicated to other blank MCU;

Power-Managed Modes:

Peripheral Highlights:

Run: CPU on, Peripherals on

Idle: CPU off, Peripherals on

Sleep: CPU off, Peripherals off

Idle mode Currents Down to 6.1 ìA Typical

Sleep mode Current Down to 0.2 ìA Typical

Timer1 Oscillator: 1 ìA, 32 kHz, 2V

Watchdog Timer: 1.7 ìA

Two-Speed Oscillator Start-up

High-Current Sink/Source 25 mA/25 mA

Three External Interrupts

One Capture/Compare/PWM (CCP) module

Enhanced Capture/Compare/PWM (ECCP) module

(40/44-pin devices only):

– One, two or four PWM outputs

– Selectable polarity

– Programmable dead time

Flexible Oscillator Structure:

· Four Crystal modes, up to 40 MHz

· 4x Phase Lock Loop (PLL) – Available for Crystal and Internal Oscillators)

· Two External RC modes, up to 4 MHz

· Two External Clock modes, up to 40 MHz

· Internal Oscillator Block:

– Fast wake from Sleep and Idle, 1 ìs typical

– 8 user-selectable frequencies, from 31 kHz to 8 MHz

– Provides a complete range of clock speeds, from 31 kHz to 32 MHz when used with PLL

– User-tunable to compensate for frequency drift

· Secondary Oscillator using Timer1 @ 32 kHz

· Fail-Safe Clock Monitor

– Auto-shutdown and auto-restart which can be applied for crack MCU memory

Master Synchronous Serial Port (MSSP) module

Supporting 3-Wire SPI (all 4 modes) and I2C™

Master and Slave modes

Enhanced Addressable USART module

– Supports RS-485, RS-232 and LIN/J2602

– RS-232 operation using internal oscillator block

– Auto-wake-up on Start bit

– Auto-Baud Detect

10-Bit, up to 11-Channel Analog-to-Digital Converter (A/D) module, up to 100 ksps

– Auto-acquisition capability

– Conversion available during Sleep

Dual Analog Comparators with Input Multiplexing

– Allows for safe shutdown if peripheral clock stops

Special Microcontroller Features:

· C Compiler Optimized Architecture with Optional Extended Instruction Set

· 100,000 Erase/Write Cycle Enhanced Flash Program Memory Typical

· 1,000,000 Erase/Write Cycle Data EEPROM Memory Typical

· Flash/Data EEPROM Retention: > 40 Years

· Self-Programmable under Software Control

· Priority Levels for Interrupts

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 41 ms to 131s

· Single-Supply 5V In-Circuit Serial Programming™ (ICSP™) via Two Pins

· In-Circuit Debug (ICD) via Two Pins

· Wide Operating Voltage Range: 2.0V to 5.5V ECAN Technology Module Features:

· Message Bit Rates up to 1 Mbps

· Conforms to CAN 2.0B Active Specification

· Fully Backward Compatible with PIC18XXX8 CAN modules

· Three Modes of Operation:

– Legacy, Enhanced Legacy, FIFO

· Three Dedicated Transmit Buffers with Prioritization

· Two Dedicated Receive Buffers

· Six Programmable Receive/Transmit Buffers

· Three Full 29-Bit Acceptance Masks

· 16 Full 29-Bit Acceptance Filters w/Dynamic Association

· DeviceNet™ Data Byte Filter Support

· Automatic Remote Frame Handling

· Advanced Error Management Features

Attack Chip PIC18F66K90 software

Attack Chip PIC18F66K90 software

Attack Chip PIC18F66K90 starts from decapsulate the microcontroller silicon package and locate the security fuse bit which has been viewed an most commonly way to crack MCU, then extract the software out from the memory;

Low-Power Features:

· Power-Managed modes:

– Run: CPU on, peripherals on

– Idle: CPU off, peripherals on

– Sleep: CPU off, peripherals off

· Two-Speed Oscillator Start-up

· Fail-Safe Clock Monitor

· Power-Saving Peripheral Module Disable (PMD)

· Ultra Low-Power Wake-up

· Fast Wake-up, 2 ms Typical

· Low-Power WDT, 300 nA Typical

· Ultra Low 50 nA Input Leakage

· Run mode Currents Down to very low 5.5 mA, Typical

· Idle mode Currents Down to very low 2.2 mA, Typical

· Sleep mode Current Down to very low 20 nA, Typical

· RTCC Current Down to very low 700 nA, Typical

· LCD Current Down to very low 300 nA, Typical

LCD Driver and Keypad Features:

· Direct LCD Panel Drive Capability:

– Can drive LCD panel while in Sleep mode

· Up to 48 Segments and 192 Pixels, Software-Selectable

· Programmable LCD Timing module:

– Multiple LCD timing sources available

– Up to four commons: static, 1/2, 1/3 or 1/4 multiplex

– Bias configuration: Static, 1/2 or 1/3

· Low-Power Resistor Bias Network for LCD

Peripheral Highlights:

· Ten or eight CCP/ECCP modules:

– Seven Capture/Compare/PWM (CCP) modules

– Three Enhanced Capture/Compare/PWM (ECCP) modules

· Eleven 8/16-Bit Timer/Counter modules:

– Timer0 – 8/16-bit timer/counter with 8-bit programmable prescaler

– Timer1,3,5,7 – 16-bit timer/counter

– Timer2,4,6,8,10,12 – 8-bit timer/counter

· Three Analog Comparators

· Configurable Reference Clock Output

· Hardware Real-Time Clock and Calendar (RTCC) module with Clock, Calendar and Alarm Functions

– Time-out from 0.5s to 1 year

· Charge Time Measurement Unit (CTMU)

– Capacitance measurement for mTouch™ Sensing

– Time measurement with 1 ns typical resolution

· High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

· Up to Four External Interrupts

· Two Master Synchronous Serial Port (MSSP) modules:

– 3/4-wire SPI (supports all four SPI modes)

– I2C™ Master and Slave mode

Special Microcontroller Features:

· Priority Levels for Interrupts

Operating Voltage Range: 1.8V to 5.5V

On-Chip 3.3V Regulator

Operating Speed up to 64 MHz

Up to 128 Kbytes On-Chip Flash Program Memory Data EEPROM of 1,024 Bytes

4K x 8 General Purpose Registers (SRAM)

10,000 Erase/Write Cycle Flash Program

Memory, Typical 1,000,000 Erase/write Cycle Data EEPROM

Memory, Typical Flash Retention 40 Years, Minimum

Three Internal Oscillators: LF-INTRC (31 kHz),

MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

Self-Programmable under Software Control

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 4 ms to 4,194s (about 70 minutes)

· In-Circuit Serial Programming™ (ICSP™) via

Two Pins

· In-Circuit Debug via Two Pins

· Programmable:

– BOR

– LVD

· Two Enhanced Addressable USART modules:

– LIN/J2602 support

– Auto-Baud Detect (ABD)

· 12-Bit A/D Converter with up to 24 Channels:

– Auto-acquisition and Sleep operation

– Differential Input mode of operation

Attack Microcontroller PIC18F66K90 Heximal

Attack Microcontroller PIC18F66K90 Heximal

Attack Microcontroller PIC18F66K90 locked memory cell include flash and eeprom, disable the security fuse bits and get access to the databus of MCU then readout the Heximal and clone content to new IC;

Low-Power Features:

· Power-Managed modes:

– Run: CPU on, peripherals on

– Idle: CPU off, peripherals on

– Sleep: CPU off, peripherals off

· Two-Speed Oscillator Start-up

· Fail-Safe Clock Monitor

· Power-Saving Peripheral Module Disable (PMD)

· Ultra Low-Power Wake-up

· Fast Wake-up, 2 ms Typical

· Low-Power WDT, 300 nA Typical

· Ultra Low 50 nA Input Leakage

· Run mode Currents Down to very low 5.5 mA, Typical

· Idle mode Currents Down to very low 2.2 mA, Typical

· Sleep mode Current Down to very low 20 nA, Typical

· RTCC Current Down to very low 700 nA, Typical

· LCD Current Down to very low 300 nA, Typical LCD Driver and Keypad Features:

· Direct LCD Panel Drive Capability:

– Can drive LCD panel while in Sleep mode

· Up to 48 Segments and 192 Pixels, Software-Selectable

· Programmable LCD Timing module:

– Multiple LCD timing sources available

– Up to four commons: static, 1/2, 1/3 or 1/4 multiplex

– Bias configuration: Static, 1/2 or 1/3

· Low-Power Resistor Bias Network for LCD Peripheral Highlights:

· Ten or eight CCP/ECCP modules:

– Seven Capture/Compare/PWM (CCP) modules

– Three Enhanced Capture/Compare/PWM (ECCP) modules

· Eleven 8/16-Bit Timer/Counter modules:

– Timer0 – 8/16-bit timer/counter with 8-bit programmable prescaler

– Timer1,3,5,7 – 16-bit timer/counter

– Timer2,4,6,8,10,12 – 8-bit timer/counter

· Three Analog Comparators

· Configurable Reference Clock Output

· Hardware Real-Time Clock and Calendar (RTCC) module with Clock, Calendar and Alarm Functions

– Time-out from 0.5s to 1 year

· Charge Time Measurement Unit (CTMU):

– Capacitance measurement for mTouch™ Sensing

– Time measurement with 1 ns typical resolution

· High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

· Up to Four External Interrupts

· Two Master Synchronous Serial Port (MSSP) modules:

– 3/4-wire SPI (supports all four SPI modes)

– I2C™ Master and Slave mode

Special Microcontroller Features:

· Priority Levels for Interrupts

Operating Voltage Range: 1.8V to 5.5V

On-Chip 3.3V Regulator

Operating Speed up to 64 MHz

Up to 128 Kbytes On-Chip Flash Program Memory Data EEPROM of 1,024 Bytes

4K x 8 General Purpose Registers (SRAM)

10,000 Erase/Write Cycle Flash Program

Memory, Typical 1,000,000 Erase/write Cycle Data EEPROM

Memory, Typical Flash Retention 40 Years, Minimum

Three Internal Oscillators: LF-INTRC (31 kHz),

MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

Self-Programmable under Software Control

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 4 ms to 4,194s (about 70 minutes)

· In-Circuit Serial Programming™ (ICSP™) via Two Pins

· In-Circuit Debug via Two Pins

· Programmable:

– BOR

– LVD

· Two Enhanced Addressable USART modules:

– LIN/J2602 support

– Auto-Baud Detect (ABD)

· 12-Bit A/D Converter with up to 24 Channels:

– Auto-acquisition and Sleep operation

– Differential Input mode of operation

Attack MCU PIC16F887 Program

Attack MCU PIC16F887 Program

Attack MCU PIC16F887 tamper resistance system and readout the Program and data from its flash memory and eeprom memory, clone firmware to new IC which will provide the same functions as original Microcontroller PIC16F887;

Module: Analog-To-Digital Converter (ADC) Module

Selecting the VP6 reference as the analog input source (CHS<3:0> = 1111) for the ADC conversion after sampling another analog channel with input voltages approximately greater than 3.6V can temporarily disturb the HFINTOSC oscillator.

4. Module: MSSP (SPI Master Mode)

With MSSP in SPI Master mode, FOSC/64 or Timer2/2 clock rate and CKE = 0, a write collision may occur if SSPBUF is loaded immediately after the transfer is complete after Attack MCU. A delay may be required after the MSSP Interrupt Flag bit, SSPIF, is set or the Buffer Full bit, BF, is set and before writing SSPBUF. If the delay is insufficiently short, a write register and NOT during the start of an actual ADC conversion using the GO/DONE bit in the ADCON0 register.

This only occurs when selecting the VP6 reference ADC channel using the CHS<3:0> bits in the ADCON0 collision may occur as indicated by the WCOL bit being set.

Select an ADC channel with input voltages lower than 3.6V prior to selecting the VP6 reference voltage input. Any analog channel can be used, even if that channel is configured as a digital I/O (configured as an output) that is driving the output pin low when Attack MCU. An alternative is to configure the CVREF module to output a voltage less than 3.6V and then selecting that analog channel CHS<3:0> = 1110 as the analog input source.

Add a software delay of one SCK period after detecting the completed transfer and prior to updating the SSPBUF contents. Verify the WCOL bit is clear after writing SSPBUF. If the WCOL is set, clear the bit in software and rewrite the SSPBUF register.

Date Codes that pertain to this issue:

All engineering and production devices.

Affected Silicon Revisions