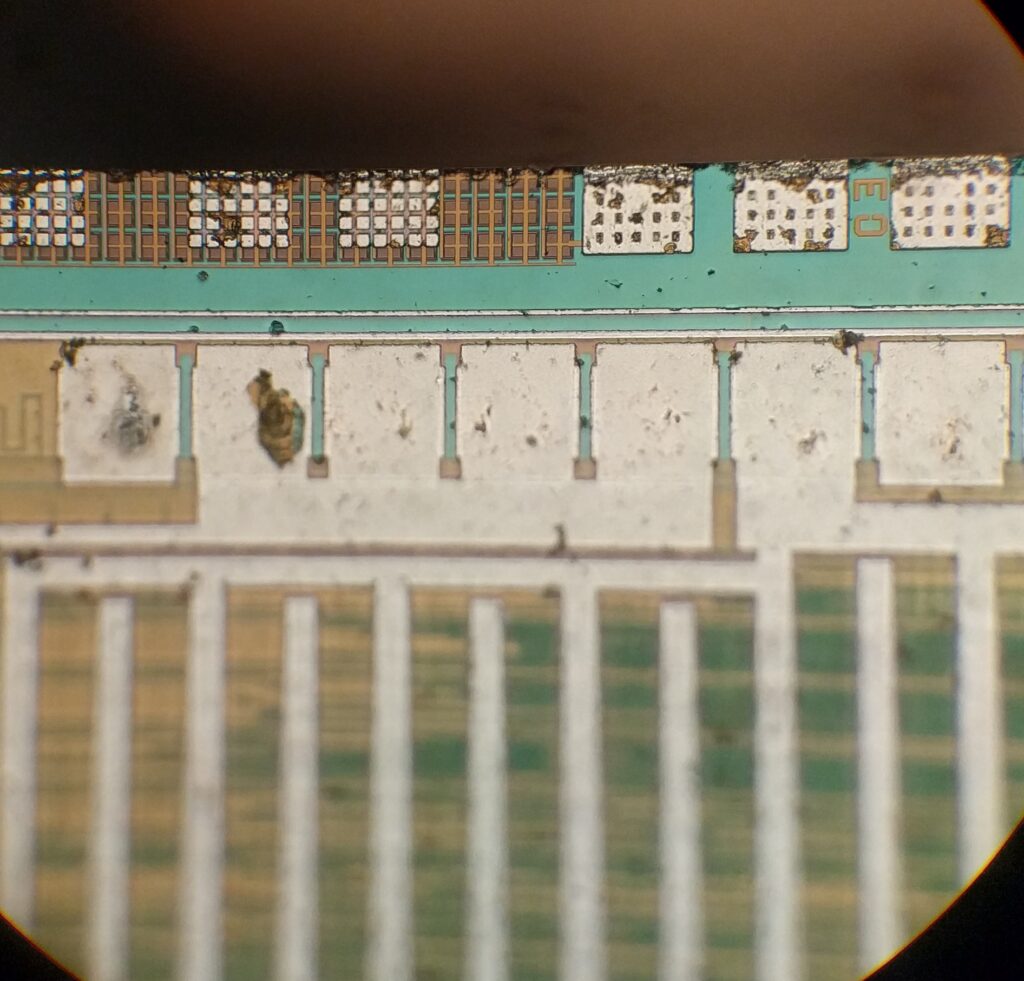

Break IC ATmegaA2560PA Heximal

Break IC ATmegaA2560PA Heximal

Break IC ATmegaa2560PA Heximal and make microcontroller atmega2560pa cloned units which will provide the same functions as original verison, the embedded firmware inside flash and eeprom memory of mcu atmega2560pa will be readout;

Each half period of the external clock applied must be longer than one system clock cycle to ensure correct sampling. The external clock must be guaranteed to have less than half the system clock frequency (fExtClk < fclk_I/O/2) given a 50/50% duty cycle.

Since the edge detector uses sampling, the maximum frequency of an external clock it can detect is half the sampling frequency (Nyquist sampling theorem). However, due to variation of the system clock frequency and duty cycle caused by Oscillator source (crystal, resonator, and capacitors) tolerances, it is recommended that maximum frequency of an external clock source is less than fclk_I/O/2.5 if Break IC heximal.

An external clock source can not be prescaled.

Bit 7 – TSM: Timer/Counter Synchronization Mode.

Writing the TSM bit to one activates the Timer/Counter Synchronization mode. In this mode, the value that is written to the PSRASY and PSRSYNC bits is kept, hence keeping the corresponding prescaler reset signals asserted.

This ensures that the corresponding Timer/Counters are halted and can be configured to the same value without the risk of one of them advancing during configuration. When the TSM bit is written to zero, the PSRASY and PSRSYNC bits are cleared by hardware, and the Timer/Counters start counting simultaneously.

Bit 0 – PSRSYNC: Prescaler Reset for Synchronous Timer/Counter

When this bit is one, Timer/Counter0 and Timer/Counter1, Timer/Counter3, Timer/Counter4 and Timer/Counter5 prescaler will be Reset. This bit is normally cleared immediately by hardware, except if the TSM bit is set. Note that Timer/Counter0,

Timer/Counter1, Timer/Counter3, Timer/Counter4 and Timer/Counter5 share the same prescaler and a reset of this prescaler will affect all timers when reading mcu atmega2560a heximal.

The Output Compare Modulator (OCM) allows generation of waveforms modulated with a carrier frequency. The modulator uses the outputs from the Output Compare Unit C of the 16-bit Timer/Counter1 and the Output Compare Unit of the 8-bit Timer/Counter0.

For more details about these Timer/Counters see “Timer/Counter0, Timer/Counter1, Timer/Counter3, Timer/Counter4, and Timer/Counter5 Prescalers” on page 169 and “8-bit Timer/Counter2 with PWM and Asynchronous Operation” on page 173 before. When the modulator is enabled, the two output compare channels are modulated together as shown in the block diagram (Figure 64).

The Output Compare unit 1C and Output Compare unit 2 shares the PB7 port pin for output. The outputs of the Output Compare units (OC1C and OC0A) overrides the normal PORTB7 Register when one of them is enabled (i.e., when COMnx1:0 is not equal to zero). When both OC1C and OC0A are enabled at the same time, the modulator is automatically enabled. The functional equivalent schematic of the modulator is shown on Figure 65. The schematic includes part of the Timer/Counter units and the port B pin 7 output driver circuit.