Archive for February, 2015

Break IC PIC16F616 Heximal

Break IC PIC16F616 Heximal

Break IC PIC16F616 Heximal starts from get some knowledge about its structure:

PIC16F616/16HV616 only:

· A/D Converter:

– 10-bit resolution

– 8 external input channels

– 2 internal reference channels

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Enhanced Capture, Compare, PWM module:

– 16-bit Capture, max. resolution 12.5 ns

– 16-bit Compare, max. resolution 200 ns

– 10-bit PWM with 1, 2 or 4 output channels, programmable “dead time”, max. frequency 20 kHz

Program Memory Organization of PIC16F616/16HV616

The PIC16F610/616/16HV610/616 has a 13-bit program counter capable of addressing an 8k x 14 program memory space. Only the first 1K x 14 (0000h-3FF) for the PIC16F610/16HV610 and the first 2K x 14 (0000h-07FFh) for the PIC16F616/16HV616 is physically implemented to facilitate the process of Recover MCU PIC16F648A Firmware.

Accessing a location above these boundaries will cause a wraparound within the first 1K x 14 space (PIC16F610/16HV610) and 2K x 14 space (PIC16F616/16HV616). The Reset vector is at 0000h and the interrupt vector is at 0004h to ease the process of MCU Cracking.

The data memory (see Figure 2-4) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank.

PIC16F610/16HV610 Register locations 40h-7Fh in Bank 0 are General Purpose Registers, implemented PC gram counter capable of addressing an 8k x 14 program memory space. Only the first 1K x 14 (0000h-3FF) for the PIC16F610/16HV610 and the first 2K x 14 (0000h-07FFh) for the PIC16F616/16HV616 is physically implemented to facilitate the process of Copy Microcontroller PIC16F737 Flash.

Accessing a location above these boundaries will cause a wraparound within the first 1K x 14 space (PIC16F610/16HV610) and 2K x 14 space (PIC16F616/16HV616). The Reset vector is at 0000h and the interrupt vector is at 0004h after Break IC PIC16F616 Heximal

Break IC PIC16F610 Binary

Break IC PIC16F610 Binary

We can break IC PIC16F610 Binary, please view the Microchip IC PIC16F610 features for your reference:

High-Performance RISC CPU:

· Only 35 instructions to learn:

– All single-cycle instructions except branches

· Operating speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt capability

· 8-level deep hardware stack

· Direct, Indirect and Relative Addressing modes

Break IC PIC16F610 Binary

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ±1%, typical

– User selectable frequency: 4 MHz or 8 MHz

· Power-Saving Sleep mode

· Voltage range:

– PIC16F610/616: 2.0V to 5.5V

– PIC16HV610/616: 2.0V to user defined maximum (see note)

· Industrial and Extended Temperature range

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Brown-out Reset (BOR)

· Watchdog Timer (WDT) with independent oscillator for reliable operation only after the process of Attack MCU PIC12F675 Binary has been completed.

· Multiplexed Master Clear with pull-up/input pin

· Programmable code protection

· High Endurance Flash:

– 100,000 write Flash endurance

– Flash retention: > 40 years for the purpose of break IC PIC16F610 Binary

Low-Power Features:

· Standby Current:

– 50 nA @ 2.0V, typical

· Operating Current:

– 20 ìA @ 32 kHz, 2.0V, typical

– 220 ìA @ 4 MHz, 2.0V, typical

· Watchdog Timer Current:

– 1 ìA @ 2.0V, typical

Peripheral Features:

· Shunt Voltage Regulator (PIC16HV610/616 only):

– 5 volt regulation

– 4 mA to 50 mA shunt range

· 11 I/O pins and 1 input only

– High current source/sink for direct LED drive

– Interrupt-on-Change pins

– Individually programmable weak pull-ups

· Analog Comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (CVREF) module (% of VDD)

– Fixed Voltage Reference

– Comparator inputs and outputs externally accessible

– SR Latch

– Built-In Hysteresis (user selectable)

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Timer1 Gate (count enable)

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

– Timer1 oscillator

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins

Break IC PIC16F690 Code

Break IC PIC16F690 Code

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register in order to Break IC PIC16F690 Code. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-9 shows the two situations for the loading of the PC.

The upper example in Figure 2-9 shows how the PC is loaded on a write to PCL (PCLATH<4:0> → PCH). The lower example in Figure 2-9 shows how the PC is loaded during aCALL or GOTO instruction (PCLATH<4:3> → PCH).

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register.

This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register to facilitate the process of Break IC PIC16C556A Software. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

ospace:none’>Figure 2-9 shows how the PC is loaded during aCALL or GOTO instruction (PCLATH<4:3> → PCH).

to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register.

Break IC PIC16F690 Code

Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0×00 in the middle of nd those being written to the PCL register. ospace:none’>Figure 2-9 shows how the PC is loaded during aCALL or GOTO instruction (PCLATH<4:3> → PCH).

the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table. For more information refer to Application Note AN556,

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing. Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually instruction (PCLATH<4:3> → PCH) can cause the problem on Copy Microcontroller PIC16CR83 Heximal.

accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register before the MCU cracking has begun.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1 address rolls over from 0xFF to 0×00 in the middle of nd those being written to the PCL register. ospace:none’>Figure 2-9 shows how the PC is loaded during aCALL or GOTO instruction (PCLATH<4:3> → PCH) for the purpose of Break IC PIC16F690 Code.

Break IC PIC16F689 Software

Break IC PIC16F689 Software

The data memory is partitioned into four banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank, in order to Break IC PIC16F689 Software, we need to figure out the location of special function register.

The General Purpose Registers, implemented as static RAM, are located in the last 96 locations of each Bank. Register locations F0h-FFh in Bank 1, 170h-17Fh in Bank 2 and 1F0h-1FFh in Bank 3 point to addresses 70h-7Fh in Bank 0.

The actual number of General Purpose Resisters (GPR) in each Bank depends on the device. Details are shown in Figures 2-4 through 2-8. All other RAM is unimplemented and returns ‘0’ when Reset Vector 0000h read. RP<1:0> of the STATUS register are the bank select bits.

Break IC PIC16F689 Software

The register file is organized as 128 x 8 in the PIC16F687 and 256 x 8 in the PIC16F689. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 “Indirect Addressing, INDF and FSR Registers”). SPECIAL FUNCTION REGISTERS:

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Tables 2-1 through 2-4). These registers are static RAM which are useful when Break Microcontroller PIC18F4220 Binary.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the “core” are described in this section. Registers related to the operation of peripheral features are described in the section of that peripheral feature.

The STATUS register, shown in Register 2-1, contains:

· the arithmetic status of the ALU

· the Reset status

· the bank select bits for data memory (GPR and SFR)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic to facilitate the process of Unlock Microcontroller. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended for the purpose.

Break IC PIC16F687 Firmware

Break IC PIC16F687 Firmware

It is also very important to understand the peripheral features when Break IC PIC16F687 Firmware

Peripheral Features:

· 17 I/O pins and 1 input only pin:

– High current source/sink for direct LED drive

– Interrupt-on-Change pin

– Individually programmable weak pull-ups

– Ultra Low-Power Wake-up (ULPWU)

· Analog Comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (CVREF) module (% of VDD)

– Comparator inputs and outputs externally accessible which can be used for Copy MCU PIC16C72 Software

– SR Latch mode

– Timer 1 Gate Sync Latch

– Fixed 0.6V VREF

· A/D Converter:

– 10-bit resolution and 12 channels

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

Break IC PIC16F687 Firmware

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Timer1 Gate (count enable)

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Enhanced Capture, Compare, PWM+ module:

– 16-bit Capture, max resolution 12.5 ns

– Compare, max resolution 200 ns

– 10-bit PWM with 1, 2 or 4 output channels, programmable “dead time”, max frequency 20 kHz

– PWM output steering control which can be manipulated to Break MCU PIC16C717 Program

· Synchronous Serial Port (SSP):

– SPI mode (Master and Slave)

· I2C™ (Master/Slave modes):

– I2C™ address mask

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins for the purpose

Program Memory Organization

The PIC16F687 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) is physically implemented for the PIC16F631, the first 2K x 14 (0000h-07FFh) for the PIC16F687, and the first 4K x 14 (0000h-0FFFh) for the PIC16F687. Accessing a location above these

boundaries will cause a wraparound. The Reset vector is at 0000h and the interrupt vector is at 0004h.

Recover MCU 12F508 Code

Recover MCU 12F508 Code

Recover MCU 12F508 Code will begin from the basic features of it:

High-Performance RISC CPU:

· Only 33 single word instructions to learn

· All instructions are single cycle (1 µs) except for program branches which are two-cycle

· Operating speed: DC – 4 MHz clock input DC – 1 µs instruction cycle.

· Power-On Reset (POR)

· Device Reset Timer (DRT)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Programmable code-protection in order to Recover Microcontroller PIC16F506 Binary

Recover MCU 12F508 Code

· 1,000,000 erase/write cycle EEPROM data memory

· EEPROM data retention > 40 years

· Power saving SLEEP mode

· Wake-up from SLEEP on pin change

· Internal weak pull-ups on I/O pins

· Internal pull-up on MCLR pin

· Selectable oscillator options:

– INTRC: Internal 4 MHz RC oscillator

– EXTRC: External low-cost RC oscillator

– XT: Standard crystal/resonator

– LP: Power saving, low frequency crystal

CMOS Technology:

· Low power, high speed CMOS EPROM/ROM technology

· Fully static design

· Wide operating voltage range

12-bit wide instructions

8-bit wide data path

Seven special function hardware registers

Two-level deep hardware stack

Direct, indirect and relative addressing modes for

· Wide temperature range:

– Commercial: 0°C to +70°C

– Industrial: -40°C to +85°C

– Extended: -40°C to +125°C

· Low power consumption

– < 2 mA @ 5V, 4 MHz

data and instructions

· Internal 4 MHz RC oscillator with programmable calibration

· In-circuit serial programming

– 15 µA typical @ 3V, 32 KHz

– < 1 µA typical standby current

Break IC PIC16C54C Firmware

Break IC PIC16C54C Firmware

Break IC PIC16C54C Firmware from both eeprom and flash, needs to disable the security fuse bits:

12-bit wide instructions

8-bit wide data path

Seven or eight special function hardware registers

Two-level deep hardware stack

Direct, indirect and relative addressing modes for

data and instructions

Peripheral Features:

· 8-bit real time clock/counter (TMR0) with 8-bit programmable prescaler

· Power-on Reset (POR)

· Device Reset Timer (DRT)

(i.e., PIC16C54 refers to PIC16C54, PIC16C54A, and PIC16C54C), unless specifically called out otherwise for the purpose of break ic.

High-Performance RISC CPU:

· Only 33 single word instructions to learn

· All instructions are single cycle except for program branches which are two-cycle

· Operating speed: DC – 40 MHz clock input DC – 100 ns instruction cycle

Break IC PIC16C54C Firmware

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Programmable Code Protection

· Power saving SLEEP mode which can be used to Break IC PIC16F88 Data

· Selectable oscillator options:

– RC: Low cost RC oscillator

– XT: Standard crystal/resonator

– HS: High speed crystal/resonator

– LP: Power saving, low frequency crystal

CMOS Technology:

· Low power, high speed CMOS EPROM/ROM technology

· Fully static design

· Wide operating voltage and temperature range:

– EPROM Commercial/Industrial 2.0V to 6.25V

– ROM Commercial/Industrial 2.0V to 6.25V

– EPROM Extended 2.5V to 6.0V

– ROM Extended 2.5V to 6.0V

· Low power consumption

– < 2 mA typical @ 5V, 4 MHz

– 15 µA typical @ 3V, 32 kHz

– < 0.6 µA typical standby current

(with WDT disabled) @ 3V, 0°C to 70°C

Note:

In this document, figure and table titles refer to all varieties of the part number indicated, (i.e., The title “Figure 15-1: Load

Conditions For Device Timing Specifications – PIC16C54A”, also refers to PIC16LC54A and PIC16LV54A parts),

Break IC PIC16F685 Flash

Break IC PIC16F685 Flash

Break IC PIC16F685 Flash needs to find out the location of this flash memory, so it is necessary to understand the structure of it:

Break IC PIC16F685 Flash

High-Performance RISC CPU:

· Only 35 instructions to learn:

– All single-cycle instructions except branches

· Operating speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt capability

· 8-level deep hardware stack

· Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ± 1%

– Software selectable frequency range of 8 MHz to 32 kHz

– Software tunable

– Two-Speed Start-up mode

– Crystal fail detect for critical applications and Break IC PIC16F873A Code

– Clock mode switching during operation for power savings

· Power-Saving Sleep mode

· Wide operating voltage range (2.0V-5.5V)

· Industrial and Extended Temperature range

· Power-on Reset (POR)

· Power-up Timer (PWRTE) and Oscillator Start-up Timer (OST)

· Brown-out Reset (BOR) with software control option

· Enhanced low-current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

· Multiplexed Master Clear/Input pin

· Programmable code protection to prevent the MCU Cracking

· High Endurance Flash/EEPROM cell:

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM retention: > 40 years

· Enhanced USART module:

– Supports RS-485, RS-232 and LIN 2.0

– Auto-Baud Detect

– Auto-wake-up on Start bit

Low-Power Features:

· Standby Current:

– 50 nA @ 2.0V, typical

· Operating Current:

– 11 ìA @ 32 kHz, 2.0V, typical

– 220 ìA @ 4 MHz, 2.0V, typical

· Watchdog Timer Current:

– <1 ìA @ 2.0V, typical for the purpose

Break IC PIC16F677 Firmware

Break IC PIC16F677 Firmware

When Break IC PIC16F677 Firmware, through manipulate the clock source mode can successfully bypass the protection mechanism of MCU and read out the firmware;

Clock Source modes can be classified as external or internal.

· External Clock modes rely on external circuitry for the clock source. Examples are: Oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

· Internal clock sources are contained internally within the Oscillator module. The Oscillator module has two internal oscillators: the 8 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC) to facilitate the process of MCU Cracking.

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bit of the OSCCON register.

Break IC PIC16F677 Firmware

If the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep after Break Chip PIC12CE518 Binary. During this time, the program counter does not increment and program execution is suspended.

The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the Oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize.

These oscillator delays are shown in Table 3-1. In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected t;mso-ansi-language: EN-US;mso-fareast-language:ZH-CN;mso-bidi-language:AR-SA’>(SCS) bit of the OSCCON register.

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 3-2 shows the pin connections for EC mode for the purpose.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC® MCU design is fully static to against Copy Microcontroller PIC16CR83 Heximal, stopping the external clock input will have the effect of halting the device while leaving all data intact.

Upon restarting the external clock, the device will resume operation as if no time had elapsed.

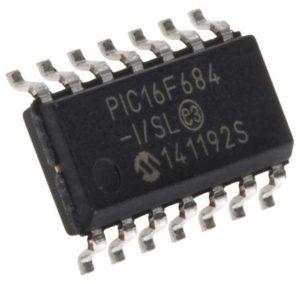

Break IC PIC16F684 Binary

Break IC PIC16F684 Binary

Let’s get some knowledge about PIC16F684 to better Break IC PIC16F684 Binary

14-Pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

High-Performance RISC CPU:

· Only 35 instructions to learn:

– All single-cycle instructions except branches

· Operating speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt capability

· 8-level deep hardware stack

Break IC PIC16F684 Binary

· Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ±1%

– Software selectable frequency range of 8 MHz to 31 kHz

– Software tunable

– Two-speed Start-up mode which is useful for Break IC PIC16F616 Heximal

– Crystal fail detect for critical applications

– Clock mode switching during operation for power savings

· Power-saving Sleep mode

· Wide operating voltage range (2.0V-5.5V)

· Industrial and Extended Temperature range

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Brown-out Detect (BOD) with software control option

· Enhanced low-current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

· Multiplexed Master Clear with pull-up/input pin

· Programmable code protection is one of the application for Break IC PIC12F609 Heximal

· High Endurance Flash/EEPROM cell:

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM retention: > 40 years

Peripheral Features:

· 12 I/O pins with individual direction control:

– High current source/sink for direct LED drive in the end

– Interrupt-on-pin change

– Individually programmable weak pull-ups

– Ultra Low-power Wake-up (ULPWU)

· Analog comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (CVREF) module (% of VDD)

– Comparator inputs and outputs externally accessible

· A/D Converter:

– 10-bit resolution and 8 channels

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Gate Input mode

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Enhanced Capture, Compare, PWM module:

– 16-bit Capture, max resolution 12.5 ns

– Compare, max resolution 200 ns

– 10-bit PWM with 1, 2 or 4 output channels, programmable “dead time”, max frequency 20 kHz

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins