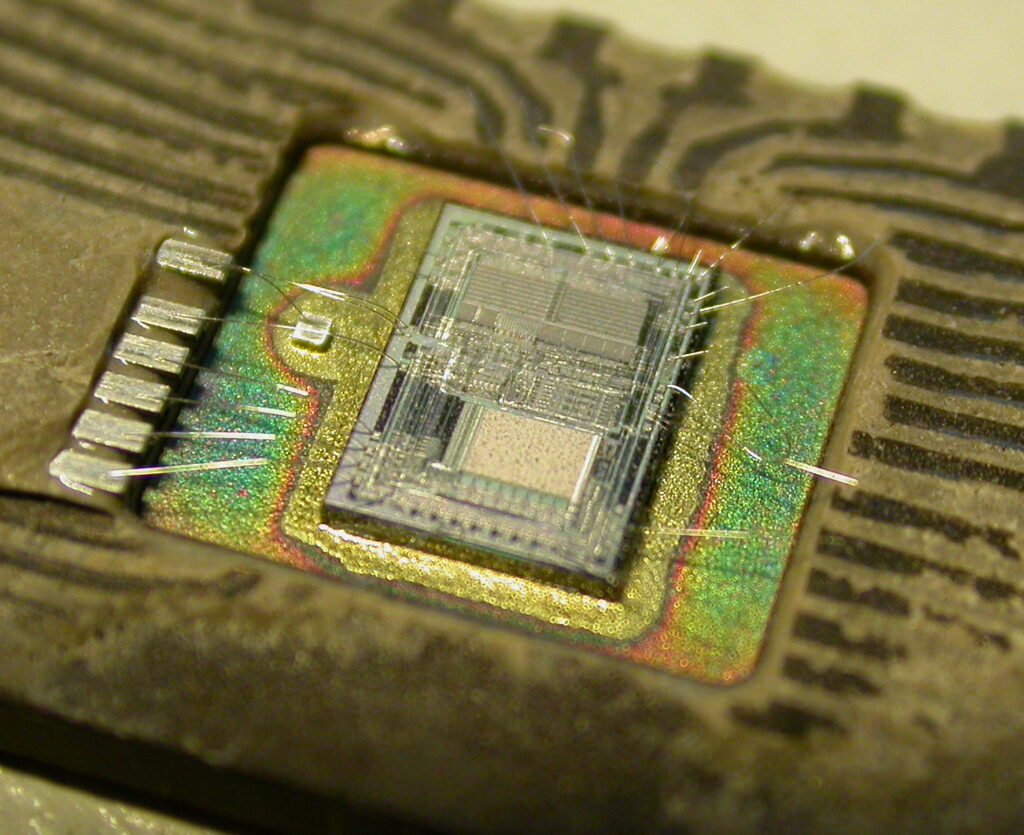

Reverse Chip ATmega162PV Heximal

Reverse Chip ATmega162PV Heximal

Reverse Chip ATmega162PV Heximal is a process to crack microcontroller atmega162pv security fuse bit and then readout the program from mcu atmega162pv flash memory and eeprom memory;

The Parity Generator calculates the parity bit for the serial frame data. When parity bit is enabled (UPMn1 = 1), the transmitter control logic inserts the parity bit between the last data bit and the first stop bit of the frame that is sent.

The disabling of the Transmitter (setting the TXEN to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted if Recover microprocessor atmega1280pa flash memory.

When disabled, the Transmitter will no longer override the TxDn pin. The USART Receiver is enabled by writing the Receive Enable (RXENn) bit in the UCSRnB Register to one.

When the Receiver is enabled, the normal pin operation of the RxDn pin is overridden by the USART and given the function as the Receiver’s serial input. The baud rate, mode of operation and frame format must be set up once before any serial reception can be done. If synchronous operation is used, the clock on the XCKn pin will be used as transfer clock when Reverse engineering mcu atmega48pv code.

The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCKn clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received.

A second stop bit will be ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer.

The receive buffer can then be reverse by reverseing the UDRn I/O location. The following code example shows a simple USART receive function based on polling of the Receive Complete (RXCn) Flag after Recover atmega88pv Chip firmware.

When using frames with less than eight bits the most significant bits of the data reverse from the UDRn will be masked to zero. The USART has to be initialized before the function can be used.