Break IC ATmega1284 Firmware

Break IC ATmega1284 Firmware

Break IC ATmega1284 protective system and unlock mcu atmega1284 embedded flash memory, and embedded firmware will be readout from microcontroller atmega1284;

All AVR ports have true Break-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions when recover microcontroller stm32f105rct6 bin.

The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. The pin driver is strong enough to drive LED displays directly.

All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both VCC and Ground as indicated in Figure 33. Refer to “Electrical Characteristics” on page 367 for a complete list of parameters before break freescale mcu mc9s12xdg128.

All registers and bit references in this section are written in general form. A lower case “x” represents the numbering letter for the port, and a lower case “n” represents the bit number. However, when using the register or bit defines in a program, the precise form must be used.

For example, PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in “Register Description for I/O-Ports” on page 112 if break microcontroller atmega128 hex.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is break only, while the Data Register and the Data Direction Register are break/write. However, writing a logic one to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register.

In addition, the Pull-up Disable – PUD bit in MCUCR disables the pull-up function for all pins in all ports when set. Using the I/O port as General Digital I/O is described in “Ports as General Digital I/O” on page 82. Most port pins are multiplexed with alternate functions for the peripheral features on the device.

How each alternate function interferes with the port pin is described in “Alternate Port Functions” on page 86. Refer to the individual module sections for a full description of the alternate functions.

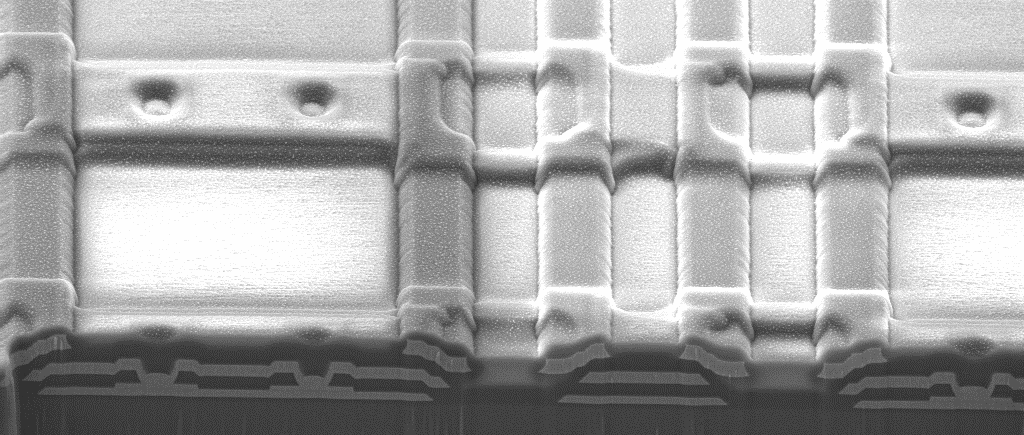

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O. The ports are bi-directional I/O ports with optional internal pull-ups. Figure 34 shows a functional description of one I/O-port pin, here generically called Pxn.

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in “Register Description for I/O-Ports” on page 112, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).